A Leading Provider of Smart, Connected and Secure Embedded Control Solutions

Microchip Proprietary and Confidential

#### Agenda

- PCIe Applications

- What is PCle?

- Microchip PCIe Solutions

- PCIe over Cable Demo

### Agenda

#### PCIe Applications

- What is PCle?

- Microchip PCle Solutions

- PCIe over Cable Demo

# Driving the Future of Automotive With Switchtec<sup>™</sup> PCle<sup>®</sup> Switches MICROCHIP Switchtec™ PCIe Switches

#### **PCle<sup>®</sup> is Everywhere**

PCIe<sup>®</sup> technology is pervasive in systems such as CPUs, GPUs, NICs, SSDs, FPGA, and other multiple end points that require low latency, high performance interconnect for diverse applications.

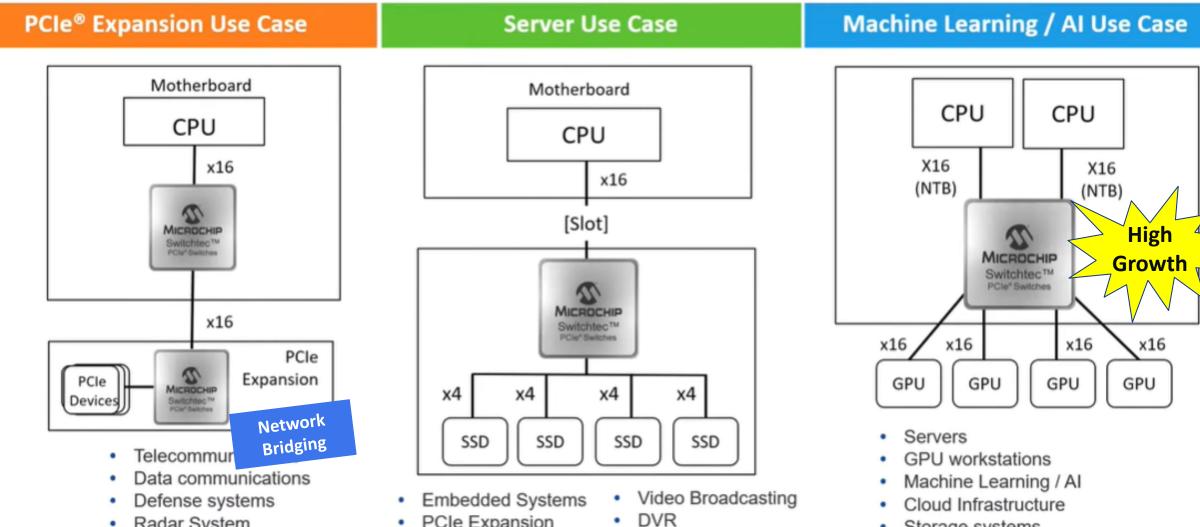

## **PCIe Fanout Switch Applications**

Radar System ٠

PCIe Expansion

Storage systems

# **PCIe Switch Application Market Segments .1**

- Server systems:

- PCIe switches are commonly used in server systems to increase the number of PCIe devices that can be connected to the system. This can include network adapters, storage controllers, and GPUs

- Data centers:

- PCIe fan out switches can be used in data centers to help manage the flow of data between multiple

PCIe devices, which can help improve overall system performance and reduce latency.

- Cloud computing:

- PCIe switches are also used in cloud computing environments to connect multiple virtual machines to a single physical PCIe device, such as a GPU, to improve the efficiency of the cloud computing environment.

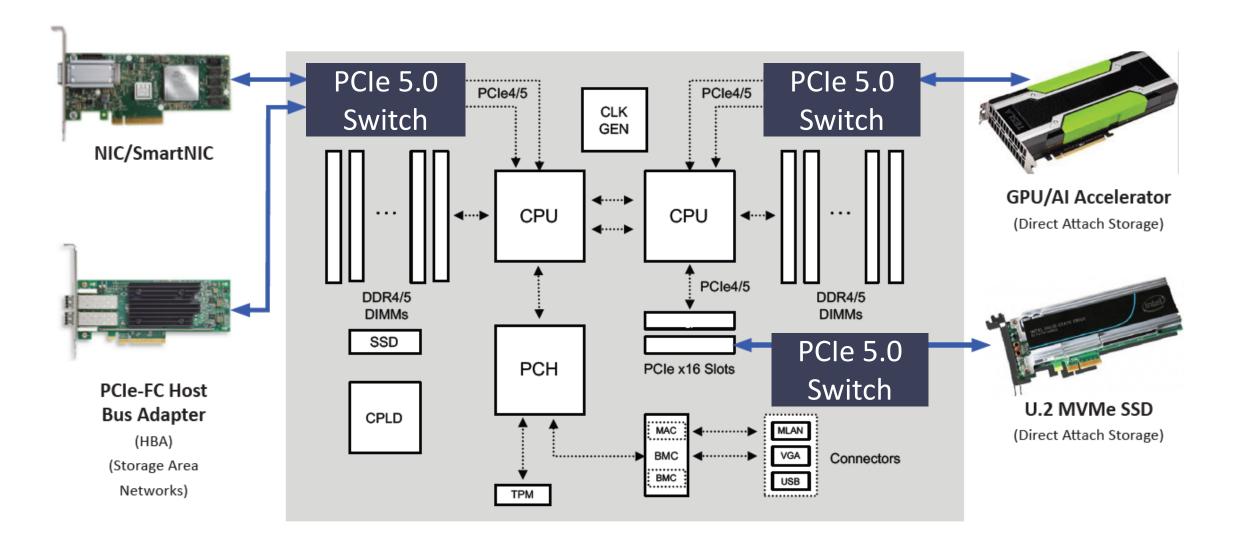

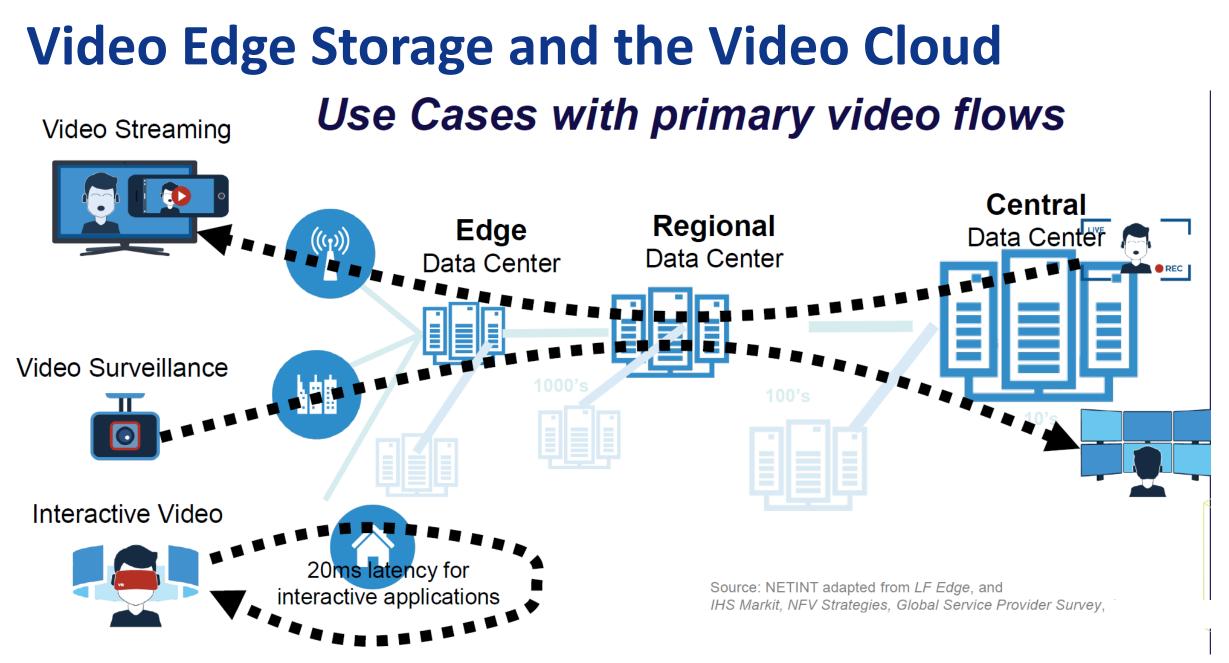

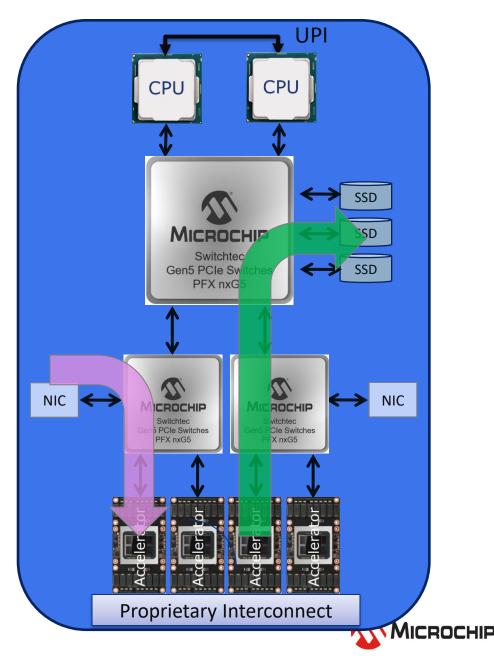

#### **Data Center Typical Application with PCIe Switches**

# PCIe Switch Application Market Segments .2

#### Media and entertainment:

PCIe switches are used with video processing/codec to facilitate data transfer from the edge to the cloud

#### Gaming systems:

PCIe switches can be used in gaming systems to connect multiple GPUs or other high-performance devices to a single PCIe slot, which can help improve gaming performance and reduce latency

#### Industrial and embedded systems:

PCIe switches are often used in industrial and embedded systems where space and power consumption are critical factors. They can help reduce the number of PCIe slots needed, which can help save space and power

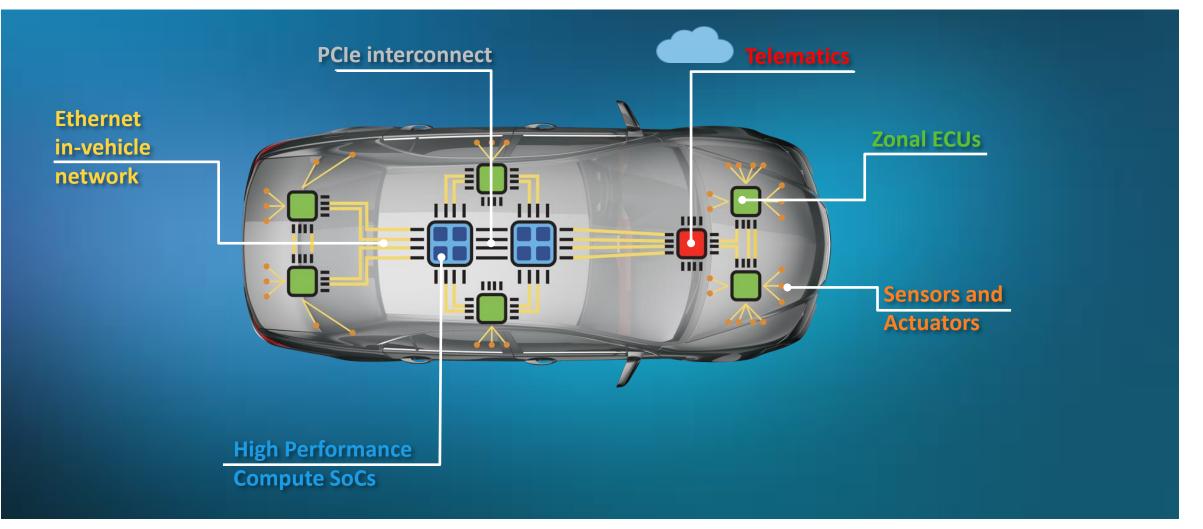

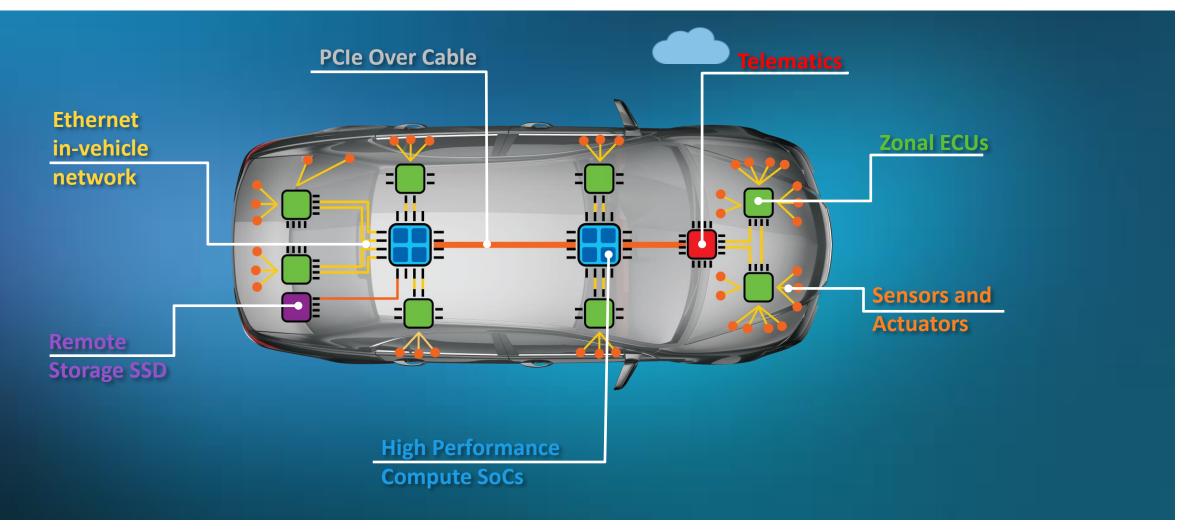

### **Future of Automotive**

#### "ultimate mobile device"

# "sensor to cloud connectivity"

#### "data-center on wheels"

# **Autonomous Mobility Drives Big Data**

- Camera/sensor data

- ECU interconnectivity

- Redundant safety networks

- Cloud connectivity

- Data logging

LiDAR, Radar

1-2Gbps

# **Why PCIe For Automotive?**

- It is a natural I/O bus that is already available in most SoCs, controllers, & CPUs.

- Open standard with a large ecosystems and multiple vendors.

- Point-to-Point architecture

- Supports chip-to-chip, backplanes, short cables and optical communication topologies.

- Extremely low latency compared to other protocols.

- Scalable bandwidth

### Agenda

- PCIe Applications

- What is PCIe?

- Microchip PCle Solutions

- PCIe over Cable Demo

# Driving the Future of Automotive With Switchtec<sup>™</sup> PCle<sup>®</sup> Switches MICROCHIP Switchtec™ PCIe Switches

# **PCI-SIG - Organizing Body**

- PCI-SIG = Peripheral Component Interconnect Special Interest Group

- Industry organization specifying

- Peripheral Component Interconnect (PCI),

- PCI-X

- PCI Express (PCIe)

- Based in Beaverton, Oregon

- Formed 1992

- Specifications are available to members of the organization <u>https://pcisig.com/specifications</u>

# **Spec History: PCIe Speed Comparison**

| PCIe<br>Generation | Encoding  | Transfer<br>Speed (GT/s) | X1<br>Throughput<br>(GB/s) | X4<br>Throughput<br>(GB/s) | X8<br>Throughput<br>(GB/s) | X16<br>Throughput<br>(GB/s) |

|--------------------|-----------|--------------------------|----------------------------|----------------------------|----------------------------|-----------------------------|

| Gen 1              | 8b/10b    | 2.5                      | 0.25                       | 1                          | 2                          | 4                           |

| Gen 2              | 8b/10b    | 5                        | .5                         | 2                          | 4                          | 8                           |

| Gen 3              | 128b/130b | 8                        | ~1                         | ~4                         | ~8                         | ~16                         |

| Gen 4              | 128b/130b | 16                       | ~2                         | ~8                         | ~16                        | ~32                         |

| Gen 5              | 128b/130b | 32                       | ~4                         | ~16                        | ~32                        | ~64                         |

Microchip Proprietary and Confidential

## **PCle Future Timeline**

| Specification in<br>Progress | Draft 0.3   | Draft 0.5      | Draft 0.7         | Draft 0.71 | Draft 0.9   | Final 1.0            |

|------------------------------|-------------|----------------|-------------------|------------|-------------|----------------------|

| 16 GT/s NRZ                  |             |                |                   |            | Morkeroup   |                      |

| PCI Express 4.0 Base         |             |                | Workgroup vote on |            | Workgroup   | WG approved on Sept. |

| Electrical Chapter           |             |                | April 7           |            | 30, 2017    | 28, 2017             |

| 32 GT/s NRZ                  |             |                |                   |            |             |                      |

| PCI Express 5.0 Base         | WG approved | WG approved on | WG approved on    |            | WG approved | WG approved on       |

| Electrical Chapter           | 5/11/17     | 10/3/17        | 03/29/18          |            | on 09/27/18 | 05/23/19             |

| 64 GT/s PAM4                 |             |                |                   |            |             |                      |

|                              | WG          | WG             | WG                | WG         | WG          | WG                   |

| PCI Express 6.0              | approved    | approved       | Approved          | Approved   | Approved    | Approved             |

| Base Electrical Chapter      | 9/12/19     | 12/12/19       | 10/08/20          | 06/24/21   | 09/30/21    | 12/16/21             |

| 128 GT/s PAM4                | WG          |                |                   |            |             |                      |

| PCI Express 7.0              | approved    |                |                   |            |             |                      |

| Base Electrical Chapter      | 03/23/23    | Dec 2023       | Mar 2025          |            | Sep 2025    | Dec 2025             |

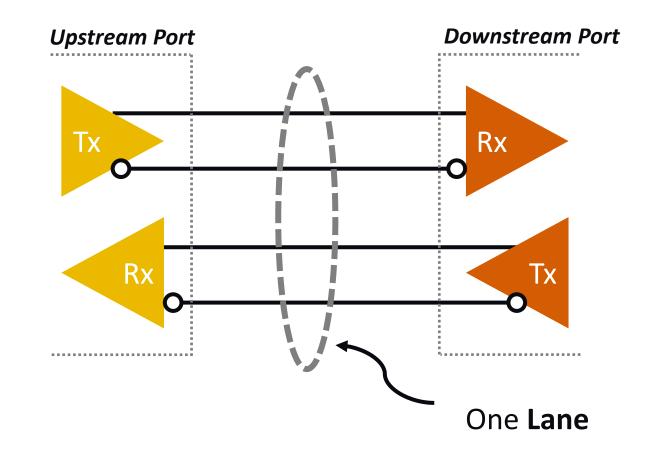

# **PCIe Elements**

- A lane includes a differential transmitter and a differential receiver, 4 wires per lane.

- A **lane** is **full-duplex** (Also regarded as dual-simplex)

- Dual-Simplex connection, transfers in both direction simultaneously

- Symmetric: A port has the same number of lanes in each direction (RX & TX)

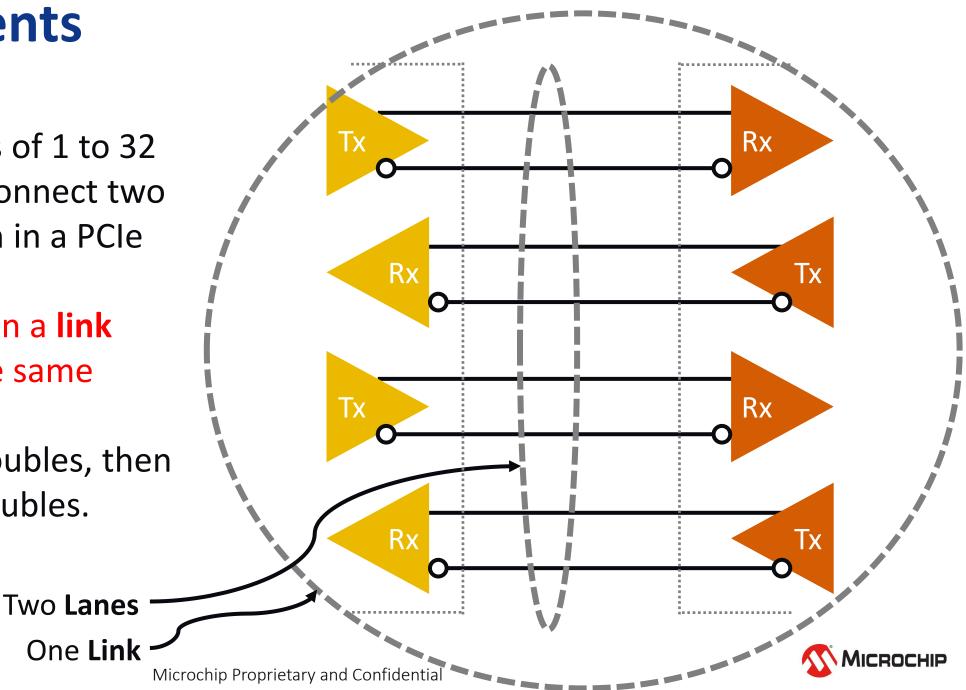

# **PCIe Elements**

- A link consists of 1 to 32

lanes which connect two devices within in a PCIe

hierarchy

- All lanes within a link operate at the same speed

- Lane count doubles, then bandwidth doubles.

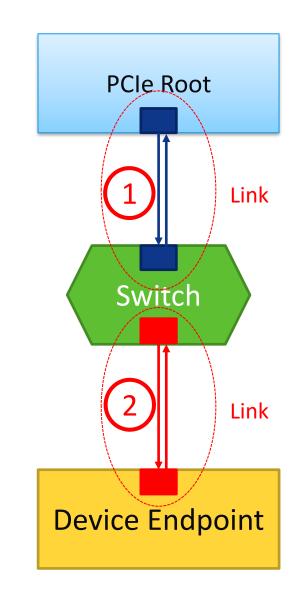

# **PCIe Systems**

PCIe Port Terminology:

- Must be viewed from each 'link perspective'

- <u>Link:</u> PHY-to-PHY Connection

- Link width can be x1, x2, x4, x8, x12, x16, x32 lanes (Bifurcation)

- Link Speed can be different at point 1 and 2.

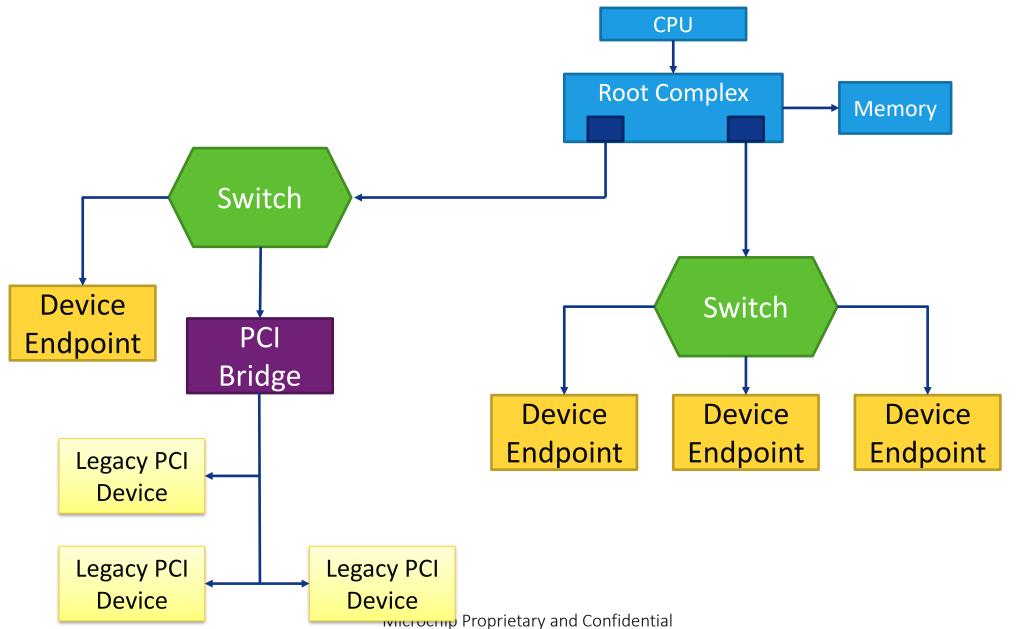

### **PCIe System Hierarchy Example**

Microchip

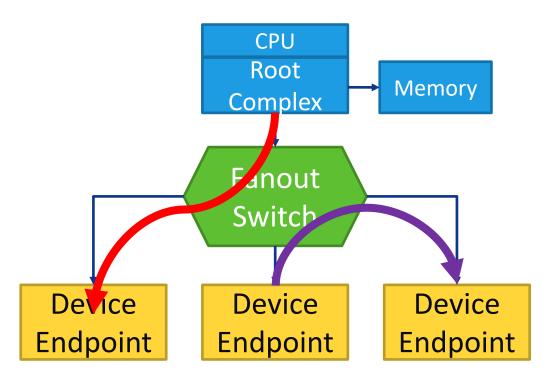

# System Component: PCIe Fanout Switches

#### PCIe switches have:

- One upstream port that connects in the direction of the host

- 1+ downstream ports that connect to the devices or additional switches

- Switching logic that routes the data packets between the ports

- Peer-to-Peer

Microchip Proprietary and Confidential

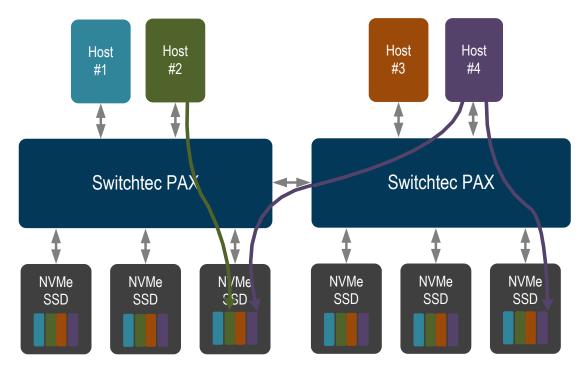

# **Peer to Peer Applications**

- Accelerator direct to storage use model

- NVMe SSDs

- NVRAM Drive

- JBOF

- NVMe RAID Controller

- SAS Controller

- Network (Infiniband, Ethernet, etc) direct to Accelerator is typically close to the Accelerators

- Switch DMA could be used for:

- Host to Host communications

- Deposit to NVRAM Drive

- Deposit to NVMe Controller Memory Buffer (CMB)

- Accelerator to Accelerator

Accelerator direct to storage NIC direct to Accelerator

Microchip Proprietary and Confidential

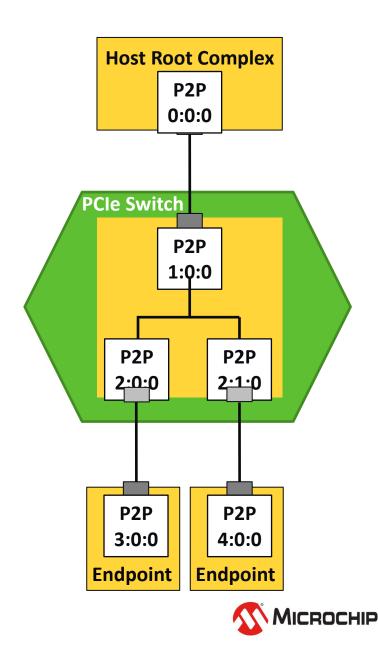

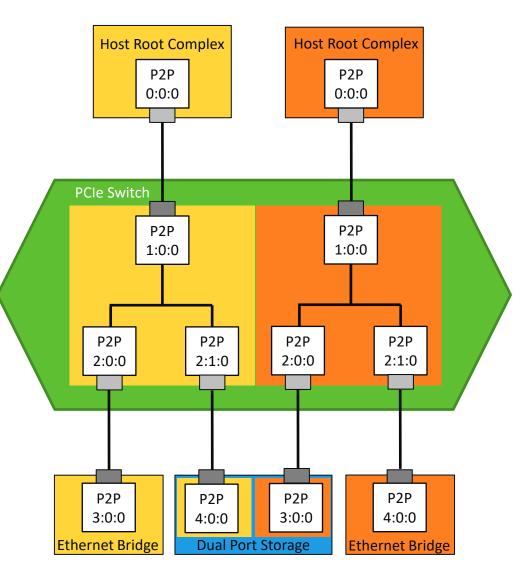

### PCIe Switch with Single-Root PCIe Enumeration

- PCIe fanout switches are a network of bridges

- Enumeration: FW/SW must go out and discover what devices and functions exist in their system.

- depth-first search algorithm to discover all BDFs.

- (Bus: Dev. Funcs) in the system starting with

0:0.0 and searching from there.

# PCIe BDF ID

- PCle enumeration/hierarchy limits

- 256 Buses per Root Complex

- 32 Devices per Bus

- 8 <u>F</u>unctions per Device

Root complex assigns and programs each device with a **Bus** # and **Device** # in its Configuration space.

After enumeration, all PCIe functions in the hierarchy have a unique "BDF" ID – you can recognize these in Linux *Ispci* output: BB:DD.F <Device\_class>: <Vendor\_name> <Function\_name>

# **PCIe Switch with Multi-Root**

#### **PCIe® Virtual Switch Partitions (VSP)**

- Divide PCIe switch into Virtual Switch Partitions.

- Each partition:

- Has its own root complex

- Is a closed system with individual enumeration and partition reset schemes

- Provides isolated memory address islands

- Dual port storage devices give transparent access to two hosts

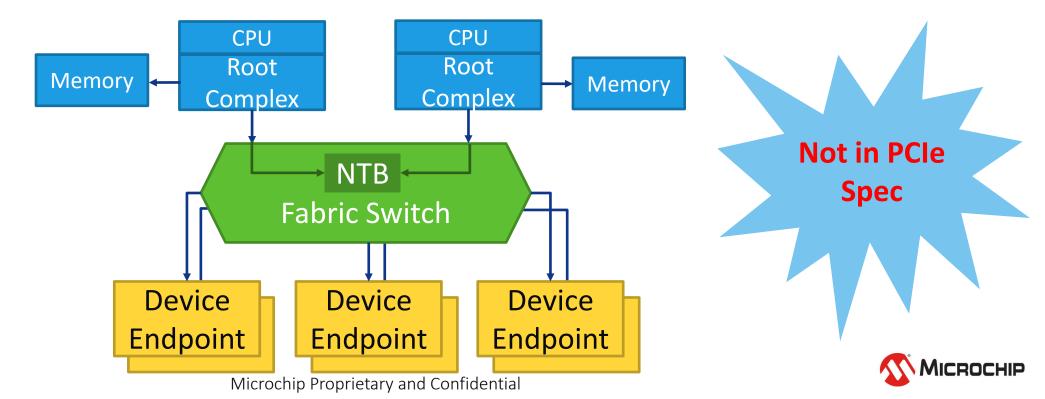

## System Component: PCIe Fanout NTB Switches

#### What about Multi-Root applications with switches?

- Switches can also allow host-to-host communication & device sharing between RCs.

- This is enabled via a feature called **NTB**: <u>Non-Transparent</u> <u>Bridging</u>.

- Requires NTB support in switch, NTB memory window configuration, and NTBspecific software on participating components to function

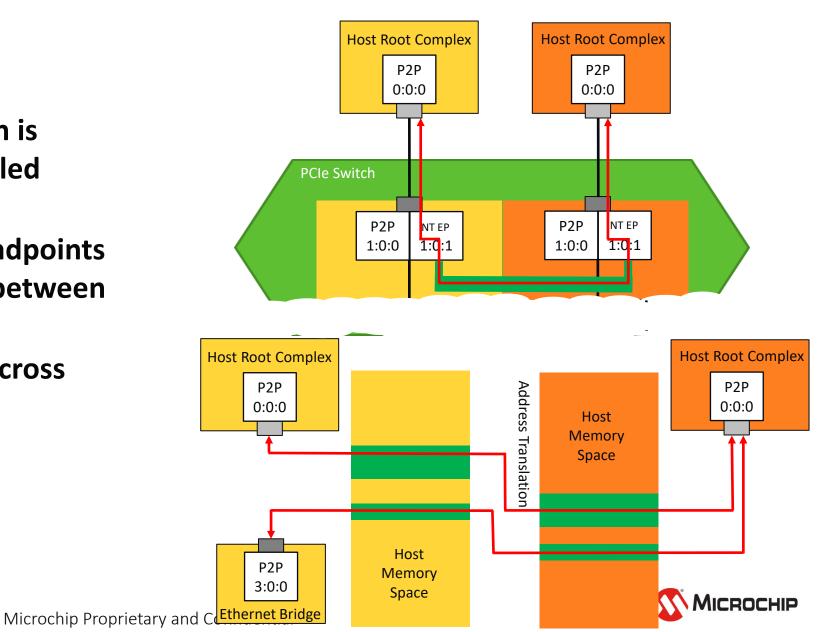

# **PCIe Switches with Non Transparent Bridging**

- "Transparent" Root complex enumerates and can access any PCIe components in the hierarchy beneath.

- "Non-transparent" The PCIe components a given root complex wants to access, exist in a hierarchy under a <u>different</u> root complex.

- In NTB-enabled switches, we call the hierarchies as "partitions" and configure rules for how RC in one partition can access RCs/devices in other partitions.

- This involves hand-crafted memory address translation rules in the NTB hardware of the switch.

# **PCIe<sup>®</sup> Non-Transparent Bridging (NTB)**

- Bridges PCIe domains

- NT End Point (NT EP) function is enumerated in each NT enabled partition

- Utilizes Non Transparent Endpoints to facilitate communication between switch partitions

- Addresses and IDs mapped across partitions

- Host-to-host communication

- Not defined in PCIe spec

### Agenda

- PCIe Applications

- What is PCle?

- Microchip PCIe Solutions

- PCIe over Cable Demo

# Driving the Future of Automotive With Switchtec<sup>™</sup> PCle<sup>®</sup> Switches MICROCHIP Switchtec<sup>™</sup> PCIe Switches

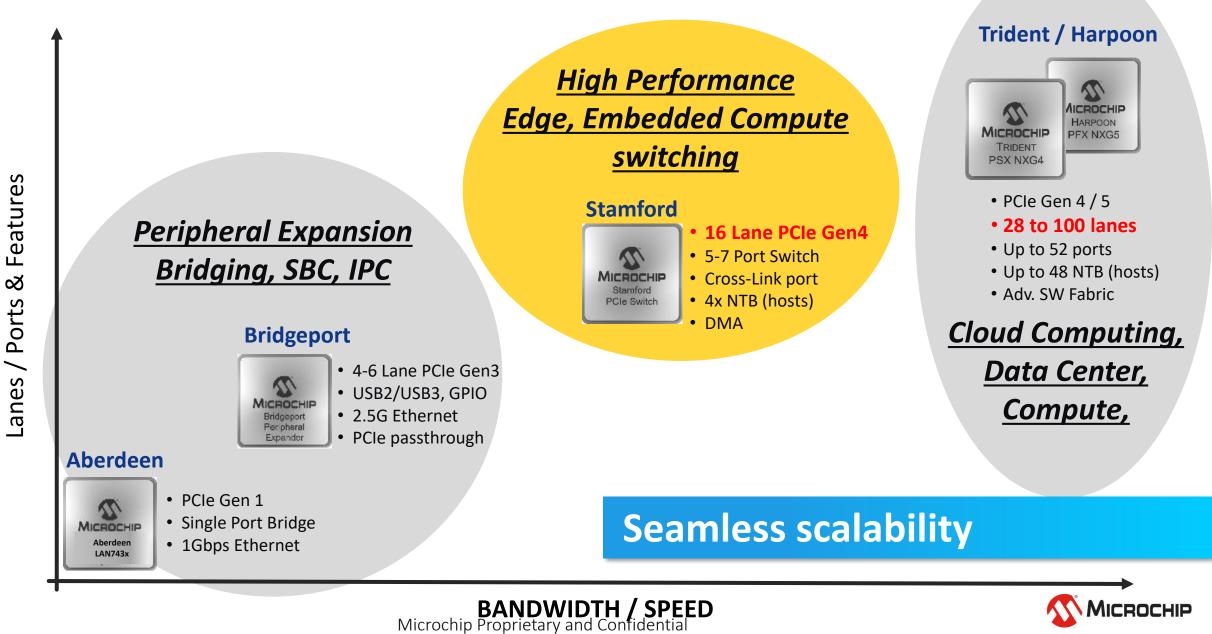

# **PCIe Roadmap Positioning**

PERFOMANCE

### **PCIe Leadership & Investment**

#### Industry's First Automotive-Qualified Gen 4 PCIe® Switches Enable Autonomous Driving Ecosystem

Switchtec<sup>™</sup> Gen 4 PCIe switches provide low-latency, low-power and highperformance connectivity for ADAS designs.

🚯 Facebook 🕑 Twitter in LinkedIn 🖾 Email < Share

CHANDLER, Ariz., February 21, 2022 — High-speed, low-latency connectivity solutions for distributed, heterogenous compute systems are a fundamental element in next-generation autonomous driving applications. Microchip Technology Inc. (Nasdaq: MCHP) is announcing the market's first Gen 4 automotive-qualified PCle<sup>®</sup> switches. These Switchtec<sup>™</sup> PFX, PSX and PAX switch solutions provide cutting-edge compute interconnect capabilities for Advanced Driver Assistance Systems (ADAS).

"Our automotive-qualified portfolio of Switchtec Gen 4 switches provides the lowest latency and high bandwidth required to link the CPU and accelerator building blocks used in ADAS applications," says Krishna Mallampati, associate director of marketing and applications for Microchip's data center solutions business unit. "We are delighted to see the culmination of several years of collaboration with key technology partners and to bring these solutions to market."

- 1<sup>st</sup> Automotive PCIe switch to market

- 1<sup>st</sup> Automotive Ethernet to market

- 1<sup>st</sup> Automotive USB to market

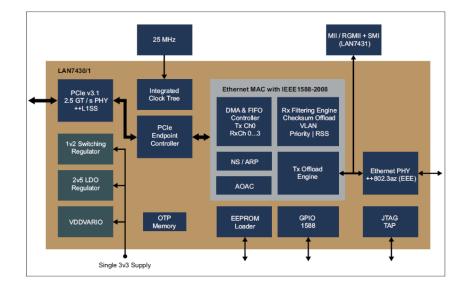

#### LAN7431 PCIe Gen3 to Gigabit Ethernet Bridge

#### **Features**

- Single-chip, PCIe 3.1 @ 2.5GT/s to 10/100/1000 Ethernet controller

- PCIe Low Power Sub States LPSS L1.1 (snooze) & L1.2 (off)

- IEEE 1588-2008 Programmable Time Compare output (Eg: 1PPS)

- IEEE 1588-2008 Capture input

- JTAG via integrated 1149.1 compliant TAP

- Accessible GPIO

- Linux, Android, MSFT Windows and QNX driver packages

- Interface to external PHY via RGMII or MII

- AEC-Q100 Grade 2 (-40 to +105C) support

- 72-pin SQFN (9 x 9 mm, 0.5mm pitch)

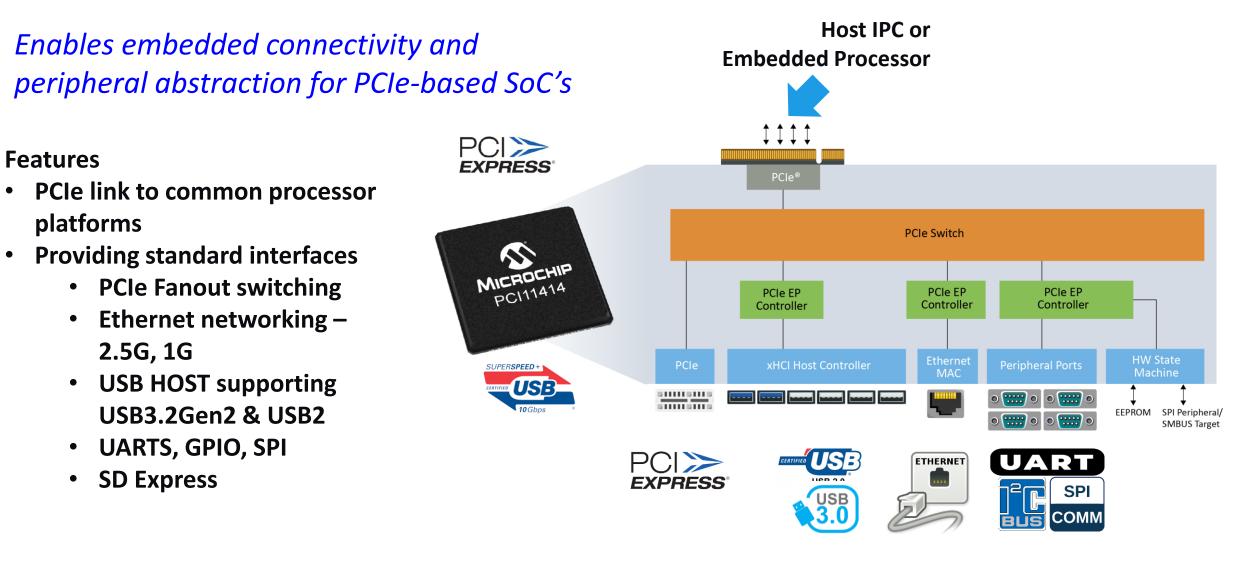

### **Bridgeport PCIe Expander Device**

#### **Bridgeport Product Family**

|                                                     | Device   | Feature  |            |          |           |            |            |       |      |  |

|-----------------------------------------------------|----------|----------|------------|----------|-----------|------------|------------|-------|------|--|

| Bridgeport CPN Feature Table                        |          | PCle     |            | USB Host |           | Networking |            |       |      |  |

| Bridgeport CPN reature Table                        |          | Upstream | Downstream |          | 3.2Gen2   | LS/FS/HS   | Networking | UARTs | GPIO |  |

|                                                     |          | Port 0   | Port 1     | Port 2   | Port 0, 1 | Port 2, 3  | MAC        |       |      |  |

| PCIe Switch – USB Host, Networking, Quad UART, GPIO | PCI11414 | •        | •          |          | •         | •          | •          |       | •    |  |

| PCIe Switch – 1 Downstream Port, USB Host           | PCI11400 | •        | •          |          | •         | •          |            | 0     | •    |  |

| PCIe Switch – 1 Downstream Port, Networking         | PCI11010 | •        | •          |          |           |            | •          | 0     | •    |  |

| PCIe Switch – 1 Downstream Port, M.2 Buildout       | PCI11101 | •        | •          |          | •         |            |            | •     | •    |  |

| PCIe Switch – 2 Downstream Port                     | PCI12000 | •        | •          | •        |           |            |            | 0     | •    |  |

#### • Industry Standard Packaging

AEC-Q100 & Automotive Grade 2 (+105degC) Commercial & Industrial (+85degC) 72QFN / 100QFN / 132DRQFN / 164DRQFN •PCle 3.1 (8GT/s) Single/Dual/Quad lanes Low Power Sub States SD Express •Networking 2.5G / 1G / 100Mb / 10Mb •USB Host Controller Type C support 10Gb Single Lane XHCI Host •Serial interfaces & GPIO RS232/RS485 (Auto direction), SPI, I2C

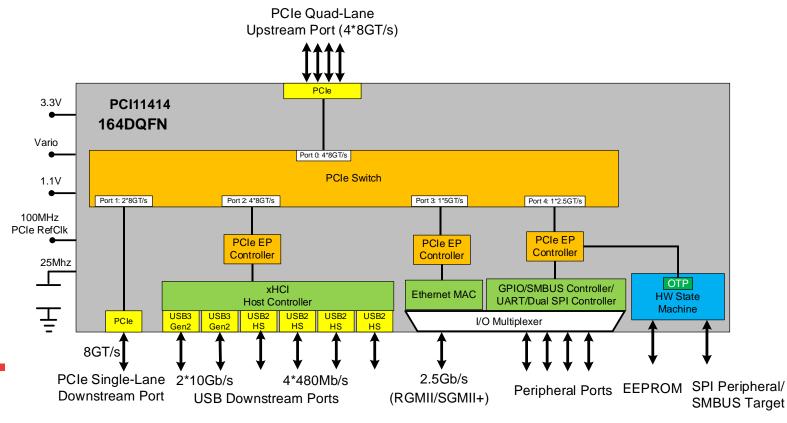

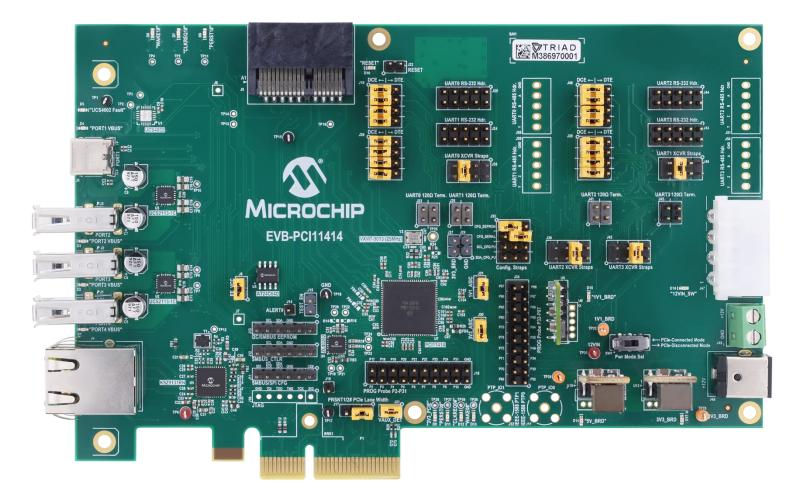

### **Evaluation Platform** EVB-PCI11414

#### Industry Standard Packaging

Commercial & Industrial (+85degC) 164DRQFN 0.5mm Pitch , 13mm x 13mm

#### •PCle 3.1 (8GT/s)

Single/Dual/Quad lanes upstream Singe lane downstream

•USB 3.2Gen2 10G XHCI Host Controller

USB Type C & 3x USB type A

#### •Ethernet 2.5G MAC

Shown here with KSZ9131 GigE PHY MAC PTP GPIO via SMA connectors

#### •Serial interfaces & GPIO

Quad RS232/RS485 (Auto direction) Dual SPI, I2C, GPIO 10bT1S /10SPE / IEEE802.3cg via SPI

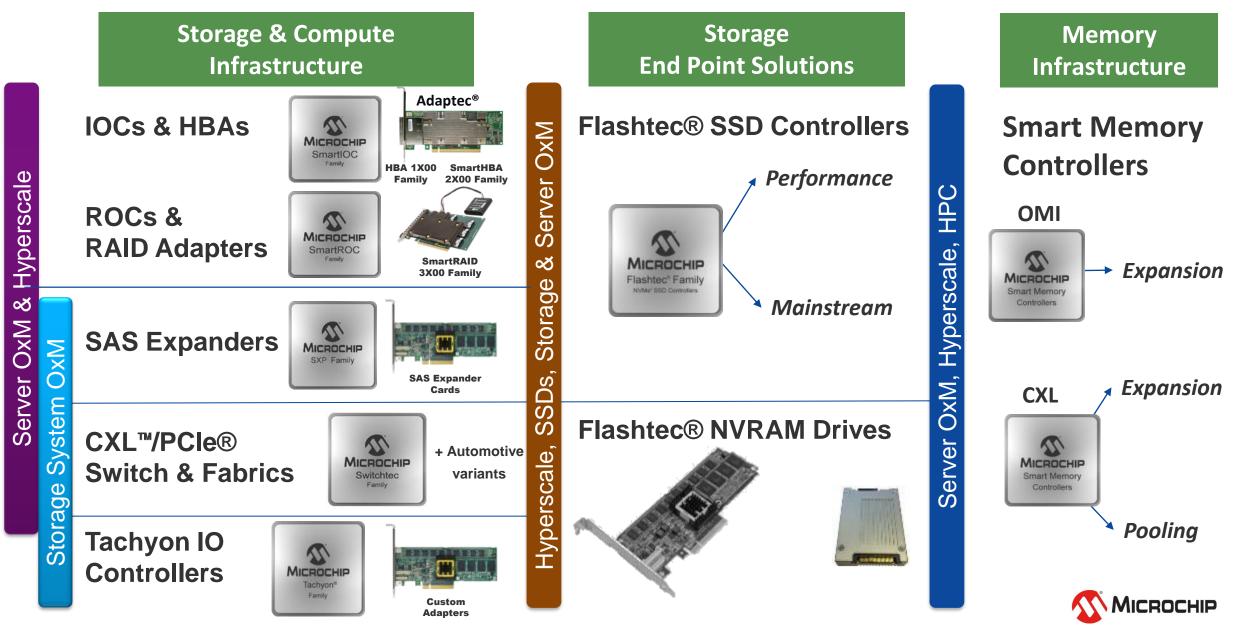

### **Microchip Data Center Solutions Segments**

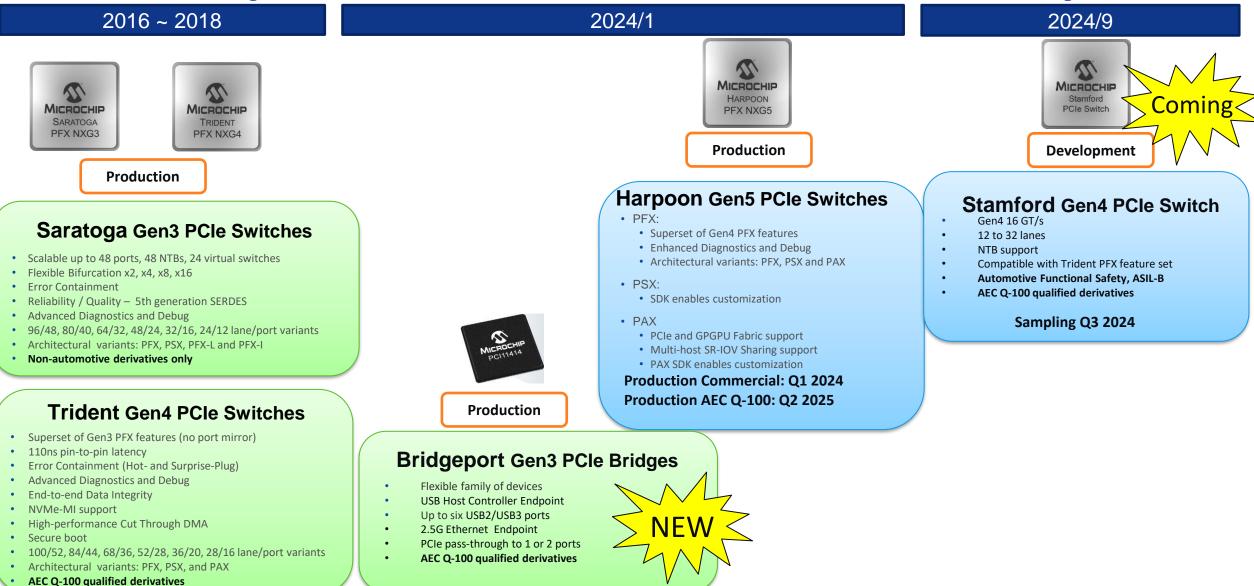

# **Microchip Embedded PCIe Switch Roadmap**

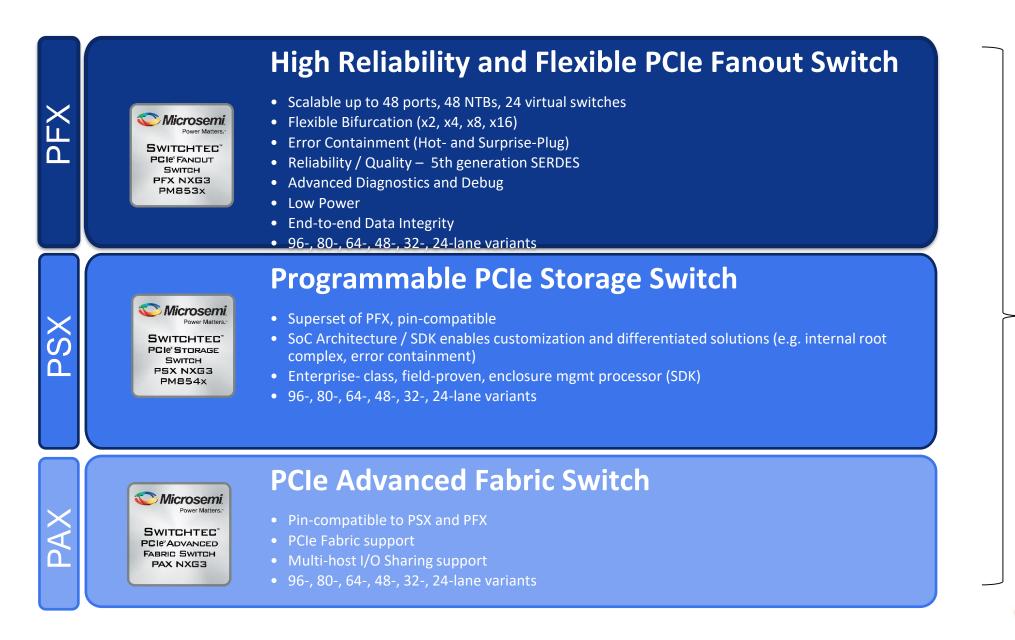

### **Switchtec PCIe Gen 3 Switch Product Family**

### **Switchtec PCIe Gen 3 Switch Product Family**

- Subset of PFX features, footprint-compatible

- Up to 24 ports, 2 NTBs, 6 virtual switches

- x4, x8, x16 port bifurcation

FX-I

$\bigcap$

Microsemi.

SWITCHTEC

PFX-L

FANOUT-LITE PCIe<sup>®</sup> SWITCH

96xG3 PM8566

\sub Microsemi

SWITCHTEC

SWITCH

**PFX-I 96xG3**

PM8576

Power Matter

- Advanced diagnostics and debug w/ chiplink gen/analyzer

- End-to-end data integrity

- 96-, 80-, 64-, 48-, 32-, 24-lane variants

#### High Reliability and Flexible PCIe Extended Temperature Industrial Fanout Switch

- Scalable up to 48 ports, 48 NTBs, 24 virtual switches

- Flexible Bifurcation (x2, x4, x8, x16)

- Error Containment (Hot- and Surprise-Plug)

- Reliability / Quality 5th generation SERDES

- Advanced Diagnostics and Debug

- Low Power

- End-to-end Data Integrity

- 96-, 80-, 64-, 48-, 32-, 24-lane variants

- PFX-I is pin compatible with the same\*\* feature set as PFX, and supports extended industrial temperature ranges -40C (Ta) to +105C (Tj)

- \*\*PFX-I doesn't support Adaptive Voltage Scaling (AVS). AVS is a way to reduce power consumption by lowering the voltage supply

and Pin-compatible across 48-32-, across and -96, 24-lane 80-, switches 64-lane

# **Trident PCIe Gen4 Switch Product Family**

- Superset of Gen3 PFX features (except no Port Mirroring)

- PCIe Gen4 Switch Scalable up to 52 ports, 48 NTBs, 26 virtual switches

- 110ns pin-to-pin latency

- Error Containment (Hot- and Surprise-Plug)

- Advanced Diagnostics and Debug

- End-to-end Data Integrity

- High-performance CutThrough DMA

- Secure boot

#### **PSX Gen4 Programmable PCIe Switch**

- Superset of Gen4 PFX

- SDK enables customization and differentiated solutions

- Enterprise- class, field-proven, enclosure mgmt processor

- NVMe-MI support

- High-performance CutThrough DMA

- Secure boot

#### **PAX Gen4 Advanced Fabric PCIe Switch**

PAX NXG4

AICBOCH

TRIDENT

PFX NXG4

TRIDENT

PSX NXG4

РFХ

PSX

PAX

• PCIe and GPGPU Fabric support

- Multi-host SR-IOV Sharing support

- High-performance CutThrough DMA and Fabric DMA

- PAX SDK enables customization and differentiated solutions

- Secure boot

across product families PFX, PSX and PAX across Pin-compatible 52-36-, and across l 28-lane 100-, switches, , 84-, 68-lane, switches, and

# Switchtec<sup>™</sup> Automotive Qualified Switch Portfolio

- Scalable up to 52 lanes, 28 ports, 26 NTBs

- 110 ns pin-to-pin latency

- Error Containment (Hot- and Surprise-Plug)

- End-to-end Data Integrity

- Secure Boot

**Part Number**

PM43028B1-F3EI

PM43036B1-F3EI

PM43052B1-F3EI

**PFX-A**

• 29 mm × 29 mm

Includes PFX attributes and,

- SDK customizable / differentiated solutions

- Enclosure management processor

- NVMe-MI support

- High-performance Cut-Through DMA

- 29 mm × 29 mm

| Part Number    | Description                                                                       | Part Number   |

|----------------|-----------------------------------------------------------------------------------|---------------|

| PM44028B1-F3EI | PSX-A 28xG4, 28-lane Gen 4<br>Programmable Automotive<br>PCIe <sup>®</sup> Switch | PM45028B1-F3E |

| PM44036B1-F3EI | PSX-A 36xG4, 36-lane Gen 4<br>Programmable Automotive<br>PCIe Switch              | PM45036B1-F3E |

| PM44052B1-F3EI | PSX-A 52xG4, 52-lane Gen 4<br>Programmable Automotive<br>PCIe Switch              | PM45052B1-F3E |

Includes PFX, PSX attributes and

- PCIe<sup>®</sup> and GPGPU Fabric support

- Multi-host Sharing of SR-IOV Endpoint

- 29 mm × 29 mm

|   | Description                                                                 | Part Number    | Description                                                |

|---|-----------------------------------------------------------------------------|----------------|------------------------------------------------------------|

| I | PFX-A 28xG4, 28-lane Gen 4<br>Fanout Automotive PCIe <sup>®</sup><br>Switch | PM44028B1-F3EI | PSX-A 28xG4, 2<br>Programmable<br>PCIe <sup>®</sup> Switch |

| I | PFX-A 36xG4, 36-lane Gen 4<br>Fanout Automotive PCIe<br>Switch              | PM44036B1-F3EI | PSX-A 36xG4, 3<br>Programmable<br>PCIe Switch              |

| I | PFX-A 52xG4, 52-lane Gen 4<br>Fanout Automotive PCle<br>Switch              | PM44052B1-F3EI | PSX-A 52xG4, 5<br>Programmable<br>PCIe Switch              |

|   |                                                                             |                |                                                            |

Description PAX-A 28xG4, 28-lane Gen 4 EL Advanced Fabric Automotive PCle<sup>®</sup> Switch PAX-A 36xG4, 36-lane Gen 4 Advanced Fabric Automotive PCIe Switch EI PAX-A 52xG4, 52-lane Gen 4 Advanced Fabric Automotive PCIe Switch CROCHIP

# **PFX/PSX/PAX Gen5 PCIe Switches**

High-Reliability, Low Latency PCIe Switches

#### **Key Features**

- PCIe Gen5 fanout switches

- 100-, 84-, 68-lane PCIe switches, 40x40mm pkg, 1mm ball pitch

- 52-, 36-, and 28-lane PCIe switches, 31x31mm pkg, 1mm ball pitch

- Flexible port bifurcation: x1\*, x2, x4, x8, x16; Upstream/Downstream/NTB

- Clocking

- SRIS, SRNS, Common clocking with SSC, SRIS clocking modes, SSC Clock Skewing

- Up to 6 Host REFCLK inputs, 7 REFCLK outputs

- Error Containment, DPC, CTS, Hot-Plug, Surprise Plug Support

- PCIe Multicast, multiple overlays per port

- Diagnostics/Debug Physical to TLP layer

- Secure boot image authentication

- Peripheral Interfaces

- TWI, SPI, UARTs, SGPIO, GPIO

- 100M/GE (on 100-, 84-lane, 68-lane devices only)

- High Performance CutThrough DMA engines

- 120 GB/sec for 4KB transfer size and 175 GB/sec for 1MB transfer size, 64 DMA channels

- PSX: customer-programmable

- SoC with Dual-Core 1GHz MIPS

- SDK, programmable PCIe Control Plane and encl. mgmt

- PAX: advanced fabric PCIe switch

- Multi-host SR-IOV sharing

- PCle Fabric Support

- Fabric DMA

- Additional new features for Gen5

- Enhanced on-chip PCIe analyzer for debugging TLPs

per port and Ordered Sets per lane

- Enhanced LTSSM monitor for advanced triggering

- Automatic port bifurcation (Rev B)

Switchtec Gen5 PCIe Switches PSX nxG5

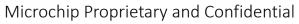

# **ChipLink on Harpoon Gen 5**

### **☑** Ease of Configuration

- Rapid device setup with presets for common use cases

- GUI-based device configuration and topology viewer

### ✓ Functional Debug

- Pattern generators and analyzers

- OS Analyzer

- TLP Analyzer: improved triggers and TLP capture

- LTSSM Monitor: improved trigger flexibility and entry tables

- Performance and Error Counters

- ☑ Signal Integrity Analysis

- Eye Capture, Signal Integrity Analyzer

- One-click forensic captures

### **☑** Complete Access to Device Documentation

Context-sensitive embedded documentation

Dramatically reduce bring-up time, and improve development efficiency

# OS Analyzer (NEW)

### Ordered Set Analyzer

- Helps debug *link training* issues PER LANE where inserting a PCIe analyzer changes the channel and ultimately may mask the issue

- Flexible filtering eliminates "analyzer garbage" and isolates transactions of interest

- Flexible cross triggering enables next level debug capability

| OS Analyzer<br>Compete with<br>Compete with<br>data<br>Up to 8192                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>Types:</b><br>TS1, TS2, FTS, CTRL, SKP                                                                                                                  | <b>Patterns</b> :<br>Any 128b Value or Mask       |  |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------|--|--|

| Contract and the second | <b>Filters:</b><br>TS1, TS2, FTS, CTRL, SKP,<br>EIEOS, EIOS, Error OS                                                                                      | Non-Repeating<br>Pattern Filter:<br>TS1, TS2, FTS |  |  |

| Egress OS<br>PEX PDIE<br>BTORAGE SWITCH<br>Egress OS<br>Egress OS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <b>Triggers</b> :<br>Tx can trigger Rx, Rx can trigger Tx, from same lane, from<br>different lane, from another block (TLP Analyzer, LTMON,<br>ARAM, GPIO) |                                                   |  |  |

\* One lane in a stack, single direction (256 entries for 16 lanes in both directions)

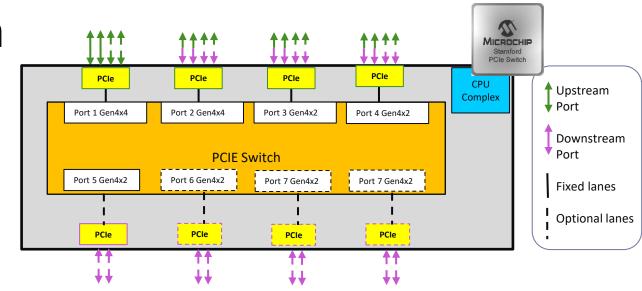

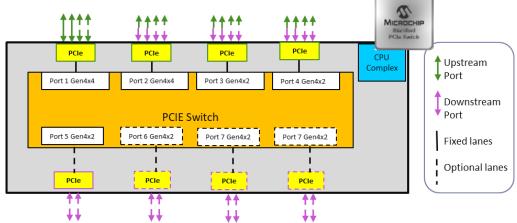

# Stamford PCIE Gen4 Switch

### with Non-Transparent Bridging

- 16-Lane PCIE Gen4 Switch

- Bifurcation x2, x4

- Up to 8 ports, pre-configured per table

- NTB Functionality on all ports

- Cross-link capability for 2x switches

- Fast data transfers: Peer-Peer / DMA

- Secure Boot & Secure Firmware Update

- ChipLink diagnostic and debug tool suite

- Commercial and Industrial temp

- Automotive Grade 2 (-40C to +105C)

- Functional Safety, ASIL-B Compliant

- Package 16mm x 16mm 353-FCBGA

- Pre-silicon emulation using Trident Evaluation Kit

- Samples September 2024

#### Stamford configuration options

| Part number                               | UFP       | DFP | NTBs | Lanes | Ports |

|-------------------------------------------|-----------|-----|------|-------|-------|

| PCI1003 8-port PCIe Gen4x16 Switch        | 2x4 + 2x2 | 2x2 | 4    | 16    | 6     |

| PCI1004 4-port PCIe Gen4x16 Switch        | 4x4       | 0   | 4    | 16    | 4     |

| PCI1001 4-port PCIe Gen4x16 Fanout Switch | 1x4       | 3x4 | 0    | 16    | 4     |

| PCI1005 7-port PCIe Gen4x16 Fanout Switch | 1x4       | 6x2 | 0    | 16    | 7     |

#### Proven IP, low risk, faster time-to-market

# **Stamford and Trident Feature Comparison**

|                          | Stamford Automotive      | Trident Automotive  |

|--------------------------|--------------------------|---------------------|

| PCIe Generation          | Gen4                     | Gen4                |

| # of Lane                | 16                       | 28/36/52            |

| # of Port                | Up to 8                  | Up to 28            |

| Multi-Host Support       | up to 4 NTBs             | up to 28 NTBs       |

| Virtual Switch Partition | Up to 4                  | Up to 14            |

| Dynamic Partitioning     | Νο                       | Yes                 |

| SR-IOV                   | NVMe Supported           | Supported with PAX  |

| DMA Engine               | Yes                      | Yes                 |

| Package                  | 353-FCBGA 16x16mm        | 753-FCBGA 29x29mm   |

| BGA ball pitch           | 0.8mm                    | 1.0mm               |

| Power Consumption        | 9W (typ) 16-lane         | 17W (typ) 28-lane   |

| Temperature              | Ta = -40 to 105degC      | Tj = -40 to 105degC |

| Functional Safety        | Compliant                | No                  |

| Tool for Configuration   | ChipLink                 | ChipLink            |

| Schedule                 | Sample in September 2024 | Production now      |

## PAX for Multi-host IO Sharing

### Key Features

- Multi-host sharing of SR-IOV and multifunction Endpoints (EPs)

- Virtualize SR-IOV NVMe SSDs to appear to each host as dedicated NVMe Controllers with a single function

- Allows host to run off-the-shelf NVMe drivers

- Combined with Fabric to provide larger systems

# **Stamford Enhanced Software Program**

#### **Datacenter Product Software**

- Firmware

- Host Applications & tools

- Secure boot

#### **Automotive Software Additions**

- Host Drivers & OS Support

- NTB Driver (2-NTB, 3-NTB and 4-NTB)

- Management Endpoint Driver

- DMA Endpoint Driver

- Linux & QNX support

- NVMe sharing software

- Virtual Root Complex

- NVMe Virtualization Manager and EP Sharing

- NVMe Inbox Driver

- Enhanced security (ACS, CMA)

- Secure boot

- Secure JTAG

- Access Control Services

- Component Measurement Authentication

- SoC interop testing (Nvidia, Qualcomm, Renesas)

### Expanded software support reduces development time

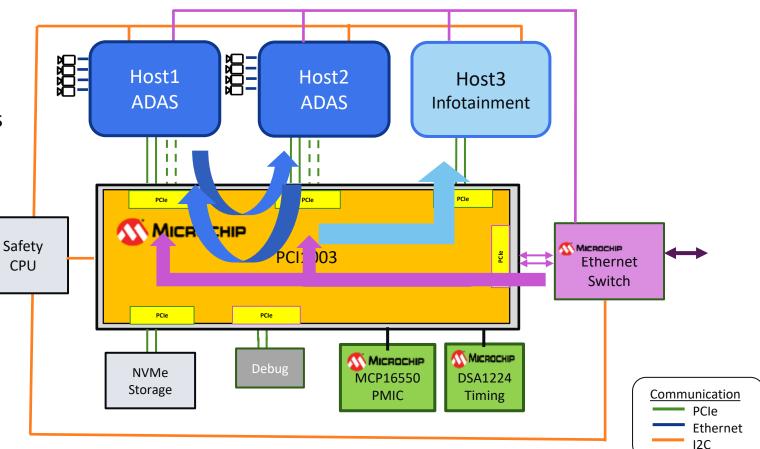

# Embedded Use Case Automotive L2+ thru L4 Driver Assist Platform

#### • Data Processing

- Image recognition / Heuristics

- Localization / perception

- Workload sharing between ADAS SoCs

- Data sharing with Infotainment SoC

- Sensor Fusion

- Driver Assist Policy

- Safety

- Component health interrogation

- System health policy

- Redundant ADAS SoC

# **Microchip PCIe Switches**

#### Hardware

- Built on 3rd Generation HW; deep expertise in signal integrity.

- Hardened IP, 8 yrs volume production at all top Cloud Datacenter, Server, and Storage providers.

- Worlds first auto grade PCIe switch announced March, 2022

- Latest generation optimized for Automotive

- Enhanced test coverage

- Flexible I/O blocks.

- Roadmap covering widest range of requirements

#### Software

- Industry leading feature set & flexibility

- Eight post-production FW releases: New features, bug fixes, maintenance

- Supported by Linux community, major OS and SoC vendors

- Six-year partnership with Dolphin Gen3-Gen4-Gen5 families

#### Support

- Dedicated local technical support

- Systems and device expertise

- SoC vendor reference designs. Proven interoperability with Qualcomm, Nvidia

- Ecosystem incl SoC, Storage, SW, & connector vendors

- Comprehensive ChipLink tool suite

#### **Reliable Supplier**

- Expanding investment in PCIe products for Automotive.

- Commitment to ISO26262

- Microchip NO EOL Policy for Long Term Automotive Support

- Top 10 WW Automotive Semiconductor Supplier

Microchip removes risks of first-generation products for safety critical applications

# **PCIe over Cable Demo**

Microchip Proprietary and Confidential - INTERNAL ONLY

# Agenda

- PCIe Applications

- What is PCle?

- Microchip PCle Solutions

- PCIe over Cable Demo

# **Driving the Future of Automotive** With Switchtec<sup>™</sup> PCle<sup>®</sup> Switches MICROCHIP Switchtec™ PCIe Switches

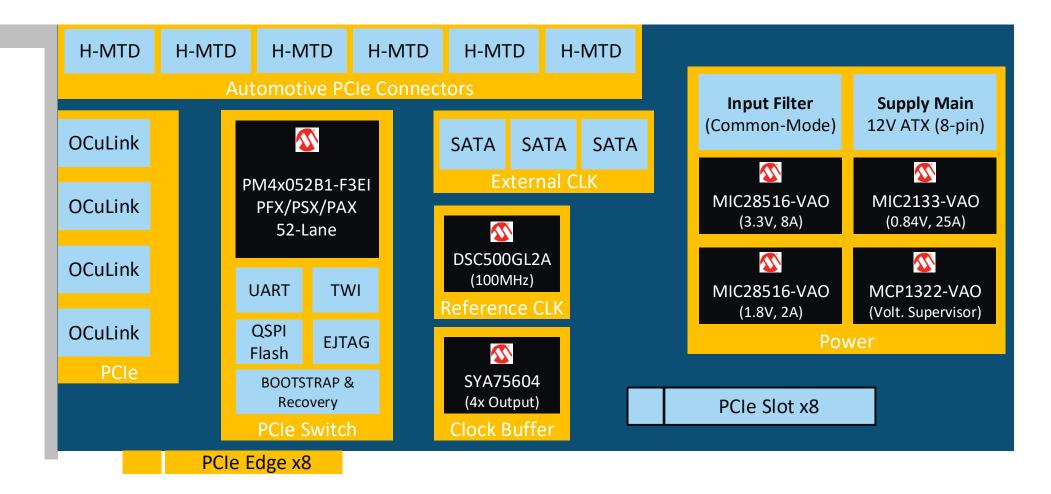

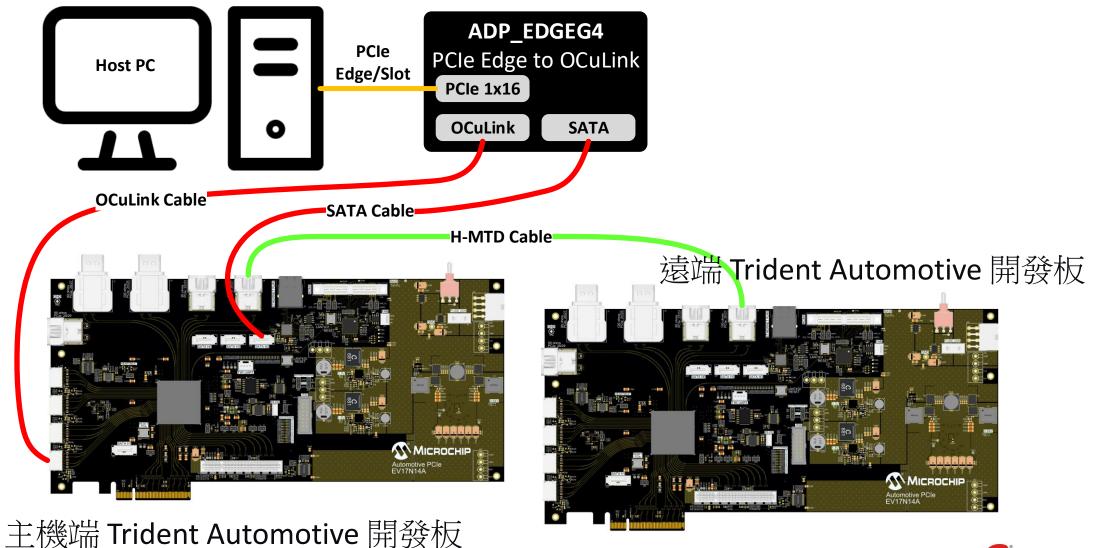

### **Automotive PCIe Reference Validation Board**

### **Microchip Total System Solution**

### Automotive PCIe Reference Validation Board H-MTD PCIe Interface Functional Check

**Міскоснір**

### **PCIe Over Cable Demo**

### **Remote Wedge Pelican Case Contents**

#### **Remote Wedge**

#### **GEMnet Cable (7m)**

#### Webcam

Toolkit

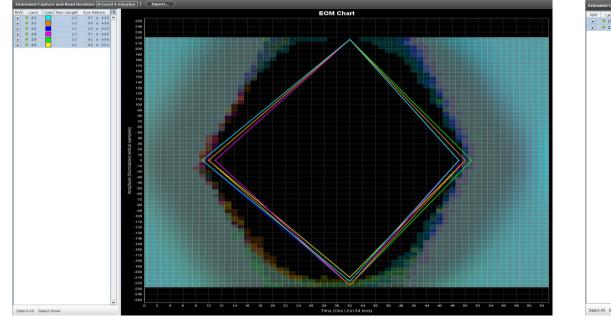

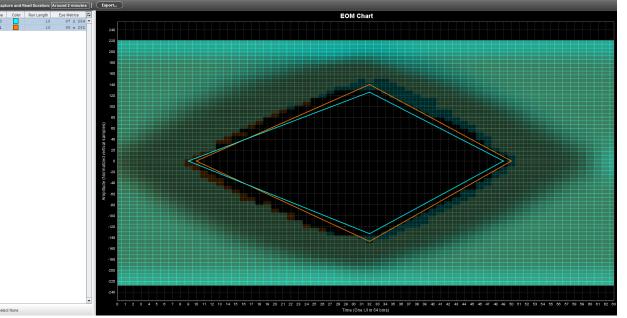

**Eye Capture Results for Different Cable Length** H-MTD PCIe Interface Functional Check

### Test Objective

Verify PCIe Performance over H-MTD

Eye Plot (Gen3 1m Cable)

Eye Plot (Gen3, 5m Cable)

# Zonal ECU with Centralized Compute Platform for ADAS Applications

# **PCIe Over Cable - End-Use Applications**

### Remote Storage Over Cable

- PCIe over cable connection to central compute SOC(s).

- SSD storage located in accessible location (trunk, interior cabin, etc.).

### Zonal Central Compute

- Distribute central compute SoCs to zonal locations.

- Adds physical location redundancy.

- Provides ECU scalability across multiple vehicle platforms.

- Reduces overall thermal load of co-locating SoCs within single module/location.

# Zonal SoCs (PCIe Over Cable) with Remote Storage for ADAS Applications

# **THANK YOU!**