# Section 27. USB On-The-Go (OTG)

## HIGHLIGHTS

This section of the manual contains the following major topics:

| 27.1  | Introduction                              |  |

|-------|-------------------------------------------|--|

| 27.2  | Control Registers                         |  |

| 27.3  | Operation                                 |  |

| 27.4  | Host Mode Operation                       |  |

| 27.5  | Interrupts                                |  |

| 27.6  | I/O Pins                                  |  |

| 27.7  | Operation in Debug and Power-Saving Modes |  |

| 27.8  | Effects of a Reset                        |  |

| 27.9  | Related Application Notes                 |  |

| 27.10 | ) Revision History                        |  |

USB On-The-Go (OTG)

27

### 27.1 INTRODUCTION

The PIC32MX USB module includes the following features:

- USB Full-Speed Support for Host and Device

- Low-Speed Host Support

- USB On-The-Go (OTG) Support

- Integrated Signaling Resistors

- Integrated Analog Comparators for VBUS Monitoring

- Integrated USB Transceiver

- Transaction Handshaking Performed by Hardware

- Endpoint Buffering Anywhere in System RAM

- Integrated Bus Master to Access System RAM and Flash

- USB module does not require the PIC32 DMA module for its operation

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded host, full-speed device, or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

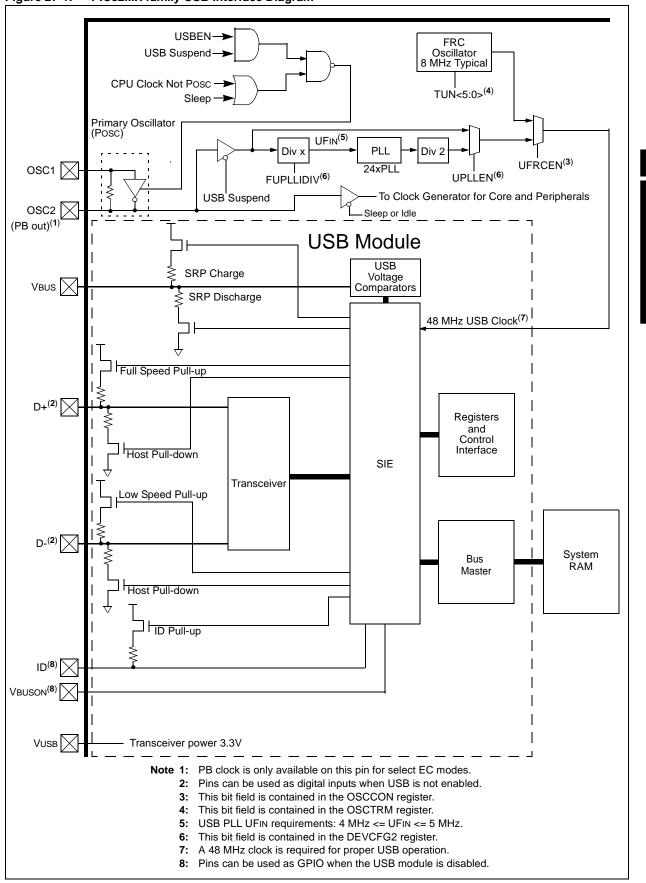

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB Bus Master, pull-up and pull-down resistors and the register interface. A block diagram of the PIC32MX USB OTG module is presented in Figure 27-1.

The clock generator provides the 48 MHz clock, which is required for USB full speed and low speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers, and generates the hardware protocol for data transfers. The USB Bus Master transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module.

**IMPORTANT:** The implementation and use of the USB specifications, as well as other third-party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

### 27.2 CONTROL REGISTERS

The USB module includes the following Special Function Registers (SFRs):

- U1OTGIR: USB OTG Interrupt Flags Register

- U1OTGIE: USB OTG Interrupt Enable Register

- U1OTGSTAT: USB Comparator and Pin Status Register

- U1OTGCON: USB Resistor and Pin Control Register

- U1PWRC: USB Power Control Register

- U1IR: USB Pending Interrupt Register

- U1IE: USB Interrupt Enable Register

- U1EIR: USB Pending Error Interrupt Register

- U1EIE: USB Interrupt Enable Register

- U1STAT: USB Status FIFO Register

- U1CON: USB Module Control Register

- U1ADDR: USB Address Register

- U1FRMH and U1FRML: USB Frame Counter Registers

- U1TOK: USB Host Control Register

- U1SOF: USB SOF Counter Register

- U1BDTP1, U1BDTP2 and U1BDTP3: USB Buffer Descriptor Table Pointer Register

- U1CNFG1: USB Debug and Idle Register

- U1EP0-U1EP15: USB Endpoint Control Register

#### 27.2.1 U1OTGIR Register

U1OTGIR (Register 27-1) records changes on the ID, data and VBUS pins, enabling software to determine which event caused an interrupt. The interrupt bits are cleared by writing a '1' to the corresponding interrupt.

#### 27.2.2 U1OTGIE Register

U1OTGIE (Register 27-2) enables the corresponding interrupt status bits defined in the U1OTGIR register to generate an interrupt.

#### 27.2.3 U1OTGSTAT Register

U1OTGSTAT (Register 27-3) provides access to the status of the VBUS voltage comparators and the debounced status of the ID pin.

#### 27.2.4 U1OTGCON Register

U1OTGCON (Register 27-4) controls the operation of the VBUS pin, and the pull-up and pull-down resistors.

#### 27.2.5 U1PWRC Register

U1PWRC (Register 27-5) controls the power-saving modes, as well as the module enable/disable control.

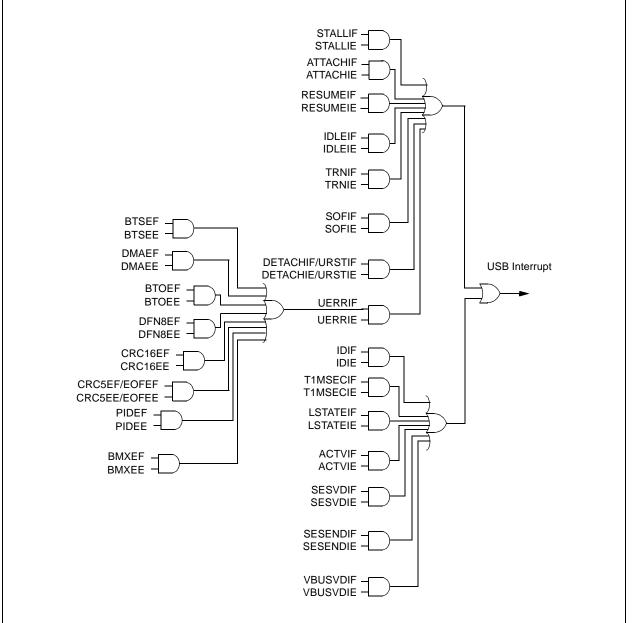

#### 27.2.6 U1IR Register

U1IR (Register 27-6) contains information on pending interrupts. Once an interrupt bit is set, it can be cleared by writing a '1' to the corresponding bit.

#### 27.2.7 U1IE Register

U1IE (Register 27-7) values provide gating of the various interrupt signals onto the USB interrupt signal. These values do not interact with the USB module. Setting any of these bits enables the corresponding interrupt source in the U1IR register.

#### 27.2.8 U1EIR Register

U1EIR (Register 27-8) contains information on pending error interrupt values. Once an interrupt bit is set, it can be cleared by writing a '1' to the corresponding bit.

#### 27.2.9 U1EIE Register

U1EIE (Register 27-9) values provide gating of the various interrupt signals onto the USB interrupt signal. These values do not interact with the USB module. Setting any of these bits enables the respective interrupt source in the U1EIR register, if UERR is also set in the U1IE register.

#### 27.2.10 U1STAT Register

U1STAT (Register 27-10) is a 16-deep First In, First Out (FIFO) register. It is read-only by the CPU and read/write by the USB module. U1STAT is only valid when the U1IR<TRNIF> bit is set.

#### 27.2.11 U1CON Register

U1CON (Register 27-11) provides miscellaneous control and information about the module.

#### 27.2.12 U1ADDR Register

U1ADDR (Register 27-12) is a read/write register from the CPU side and read-only from the USB module side. Although the register values affect the settings of the USB module, the content of the registers does not change during access.

In Device mode, this address defines the USB device address as assigned by the host during the SETUP phase. The firmware writes the address in response to the SETUP request. The address is automatically reset when a USB bus Reset is detected. In Host mode, the module transmits the address provided in this register with the corresponding token packet. This allows the USB module to uniquely address the connected device.

#### 27.2.13 U1FRMH and U1FRML Registers

U1FRMH and U1FRML (Register 27-13 and Register 27-14) are read-only registers. The frame number is formed by concatenating the two 8-bit registers. The high-order byte is in the U1FRMH register, and the low-order byte is in U1FRML.

#### 27.2.14 U1TOK Register

U1TOK (Register 27-15) is a read/write register required when the module operates as a host. It is used to specify the token type, PID<3:0> (Packet ID), and the endpoint, EP<3:0>, being addressed by the host processor. Writing to this register triggers a host transaction.

#### 27.2.15 U1SOF Register

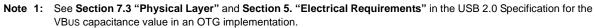

U1SOF (Register 27-16) threshold is a read/write register that contains the count bits of the Start-of-Frame (SOF) threshold value, and are used in Host mode only.

To prevent colliding a packet data with the SOF token that is sent every 1 ms, the USB module will not send any new transactions within the last U1SOF byte times. The USB module will complete any transactions that are in progress. In Host mode, the SOF interrupt occurs when this threshold is reached, not when the SOF occurs. In Device mode, the interrupt occurs when a SOF is received. Transactions started within the SOF threshold are held by the USB module until after the SOF token is sent.

#### 27.2.16 U1BDTP1, U1BDTP2 and U1BDTP3

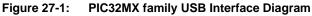

These registers (Register 27-17, Register 27-18 and Register 27-19) are read/write registers that define the upper 23 bits of the 32-bit base address of the Buffer Descriptor Table (BDT) in the system memory. The BDT is forced to be 512 byte-aligned. This register allows relocation of the BDT in real time.

#### 27.2.17 U1CNFG1 Register

U1CNFG1 (Register 27-20) is a read/write register that controls the Debug and Idle behavior of the module. The register must be preprogrammed prior to enabling the module.

#### 27.2.18 U1EP0 - U1EP15

These registers (Register 27-21) control the behavior of the corresponding endpoint.

#### 27.2.19 Associated Registers

Refer to **Section 6. "Oscillators"** (DS61112) for information on the register bits used to enable the USB PLL and/or USB FRC clock sources.

Refer to **Section 8. "Interrupts"** (DS61108) for information on the register bits used to enable and identify the USB module interrupts.

Refer to **Section 32. "Configuration"** (DS61124) for information on the configuration bits used to enable the USB PLL and set the appropriate divisor. This section also describes the bits that can be used to reclaim the USBID and VBUSON pins if the USB module will only be operated in a mode that does not require them.

#### 27.2.20 Clearing USB OTG Interrupts

Unlike other device-level interrupts, the USB OTG interrupt status flags are not freely writable in software. All USB OTG flag bits are implemented as hardware-set-only bits. These bits can only be cleared in software by writing a '1' to their locations. Writing a '0' to a flag bit has no effect.

**Note:** Throughout this section, a bit that can only be cleared by writing a '1' to its location is referred to as "Write '1' to clear bit". In register descriptions, this function is indicated by the descriptor 'K'.

| Table 2           | 7-1: USB         | Regist       | er Summa          | ry                | n                 | n                 |                        |                   |                  |                    |

|-------------------|------------------|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|--------------------|

| Address<br>Offset | Register<br>Name | Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0   |

| 0x0040            | U1OTGIR          | 31:24        | —                 |                   | —                 | —                 |                        |                   | _                | _                  |

|                   |                  | 23:16        | —                 | -                 | —                 | —                 | —                      | -                 | —                | —                  |

|                   |                  | 15:8         | _                 | _                 | —                 | —                 | _                      | —                 | —                | _                  |

|                   |                  | 7:0          | IDIF              | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF                | SESENDIF          | —                | VBUSVDIF           |

| 0x0050            | U1OTGIE          | 31:24        | _                 | -                 | —                 | —                 | _                      | -                 | —                | _                  |

|                   |                  | 23:16        | _                 | _                 | —                 | —                 | _                      | —                 | —                | _                  |

|                   |                  | 15:8         | -                 | —                 | —                 | —                 | _                      | _                 | —                | _                  |

|                   |                  | 7:0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE                | SESENDIE          | —                | VBUSVDIE           |

| 0x0060            | U1OTGSTAT        | 31:24        | _                 | _                 | —                 | —                 | _                      | _                 | —                | _                  |

|                   |                  | 23:16        | _                 | _                 | —                 | _                 |                        | _                 | _                | _                  |

|                   |                  | 15:8         | _                 | _                 | _                 | _                 |                        | _                 | _                | _                  |

|                   |                  | 7:0          | ID                | _                 | LSTATE            | _                 | SESVD                  | SESEND            | _                | VBUSVD             |

| 0x0070            | U10TGCON         | 31:24        | _                 | _                 | —                 | —                 | —                      | _                 | —                | —                  |

|                   |                  | 23:16        | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                  |

|                   |                  | 15:8         | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                  |

|                   |                  | 7:0          | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON                 | OTGEN             | VBUSCHG          | VBUSDIS            |

| 0x0080            | U1PWRC           | 31:24        | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                  |

|                   |                  | 23:16        | _                 | _                 | _                 | _                 |                        | _                 | _                | _                  |

|                   |                  | 15:8         | _                 | _                 | _                 | _                 |                        | _                 |                  | _                  |

|                   |                  | 7:0          | UACTPND           | _                 |                   | USLPGRD           | USBBUSY <sup>(1)</sup> | _                 | USUSPEND         | USBPWR             |

| 0x0200            | U1IR             | 31:24        | _                 | _                 |                   | _                 | _                      | _                 | _                | _                  |

|                   | -                | 23:16        | _                 | _                 |                   |                   |                        | _                 | _                |                    |

|                   |                  | 15:8         | _                 | _                 |                   |                   |                        |                   |                  |                    |

|                   |                  | 7:0          | STALLIF           | ATTACHIF          | RESUMEIF          | IDLEIF            | TRNIF                  | SOFIF             | UERRIF           | URSTIF<br>DETACHIF |

| 0x0210            | U1IE             | 31:24        | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                  |

| 0.0210            | 0.112            | 23:16        |                   |                   |                   |                   |                        |                   |                  |                    |

|                   |                  | 15:8         |                   |                   |                   |                   |                        |                   |                  |                    |

|                   |                  | 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            | TRNIE                  | SOFIE             | UERRIE           | URSTIE             |

| 0x0220            | U1EIR            | 31:24        | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                  |

| ONOLLO            | 0 ILIII          | 23:16        |                   |                   | _                 |                   |                        | _                 | _                |                    |

|                   |                  | 15:8         |                   |                   |                   |                   |                        |                   |                  |                    |

|                   |                  | 7:0          | BTSEF             | BMXEF             | DMAEF             | BTOEF             | DFN8EF                 | CRC16EF           | CRC5EF<br>EOFEF  | PIDEF              |

| 0x0230            | U1EIE            | 31:24        | _                 | _                 | _                 | _                 | _                      | _                 | -                | _                  |

| 0.0200            | OTELE            | 23:16        |                   |                   |                   |                   |                        | _                 | _                |                    |

|                   |                  | 15:8         |                   |                   | _                 |                   |                        |                   |                  |                    |

|                   |                  | 7:0          |                   | BMXEE             | DMAEE             | BTOEE             | DFN8EE                 | CRC16EE           | CRC5EE<br>EOFEE  | PIDEE              |

| 0x0240            | U1STAT           | 31:24        | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                  |

|                   |                  | 23:16        | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                  |

|                   |                  | 15:8         | _                 |                   | _                 | _                 |                        |                   | _                | _                  |

|                   |                  | 7:0          |                   | ENDP              | T<3:0>            | 1                 | DIR                    | PPBI              | _                | _                  |

| 0x0250            | U1CON            | 31:24        | _                 | _                 |                   | _                 | _                      | _                 |                  | _                  |

|                   |                  | 23:16        |                   | _                 | _                 | _                 | _                      | _                 | _                |                    |

|                   |                  | 15:8         | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                  |

|                   |                  | 7:0          | JSTATE            | SE0               | PKTDIS            | USBRST            | HOSTEN                 | RESUME            | PPBRST           | USBEN              |

| 00000             |                  | 01.01        |                   |                   | TOKBUSY           |                   |                        |                   |                  | SOFEN              |

| 0x0260            | U1ADDR           | 31:24        |                   |                   | _                 | _                 | _                      | _                 | _                | _                  |

|                   |                  | 23:16        | _                 | _                 | —                 | —                 | _                      | _                 | —                | _                  |

| I                 |                  | 15:8         | -                 | —                 | —                 | —                 | —                      | _                 | _                | —                  |

|                   |                  | 7:0          | LSPDEN            |                   |                   | I                 | DEVADDR<6:             | )>                |                  |                    |

Table 27-1: USB Register Summary

Legend:

- = unimplemented, read as '0'. Address offset values are shown in hexadecimal.

**Note** 1: This bit is not available on all devices. Refer to the specific device data sheet for details.

| Address<br>Offset | Register<br>Name | Bit            | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit         | Bit<br>27/19/11/3 | Bit        | Bit        | Bit                    |

|-------------------|------------------|----------------|-------------------|-------------------|-------------------|-------------|-------------------|------------|------------|------------------------|

| 0x0270            | U1BDTP1          | Range<br>31:24 |                   |                   |                   | 28/20/12/4  |                   | 26/18/10/2 | 25/17/9/1  | 24/16/8/0              |

| 0x0270            | OIBDIFI          | 23:16          | _                 |                   |                   |             |                   |            |            |                        |

|                   |                  | 15:8           |                   |                   |                   |             |                   |            |            | _                      |

|                   |                  | 7:0            |                   | —                 | F                 | DTPTRL<15:9 |                   |            | —          |                        |

| 0x0280            | U1FRML           | 31:24          |                   |                   |                   |             | _                 | _          | _          |                        |

| 0x0200            |                  | 23:16          |                   |                   |                   |             |                   |            |            |                        |

|                   |                  | 15:8           |                   |                   |                   |             |                   |            |            |                        |

|                   |                  | 7:0            |                   |                   |                   |             | L<7:0>            |            |            |                        |

| 0x0290            | U1FRMH           | 31:24          | _                 | _                 | _                 |             |                   | _          | _          |                        |

| 0x0290            |                  | 23:16          |                   |                   |                   |             |                   |            |            |                        |

|                   |                  | 15:8           |                   |                   |                   |             |                   |            |            |                        |

|                   |                  | 7:0            |                   |                   |                   |             |                   | _          | FRMH<2:0>  | _                      |

| 0x02A0            | U1TOK            | 31:24          |                   |                   |                   |             |                   | _          |            | ,<br>  _               |

| UXUZAU            | UTIOK            |                |                   |                   |                   |             |                   |            |            |                        |

|                   |                  | 23:16          | _                 | _                 | _                 |             |                   |            |            | _                      |

|                   |                  | 15:8<br>7:0    | _                 | —                 |                   | —           | _                 |            | —<br><3:0> | —                      |

| 000000            | U1SOF            |                |                   |                   |                   |             |                   |            | <3:0>      |                        |

| 0x02B0            | UISOF            | 31:24          |                   | _                 | _                 |             |                   | _          |            | -                      |

|                   |                  | 23:16          | _                 |                   | _                 |             |                   |            | _          |                        |

|                   |                  | 15:8           | —                 | —                 | _                 | -           |                   | —          | —          | —                      |

|                   |                  | 7:0            |                   |                   |                   |             | <7:0>             |            |            |                        |

| 0x02C0            | U1BDTP2          | 31:24          | _                 | _                 | _                 | _           | _                 | _          |            | —                      |

|                   |                  | 23:16          | _                 | _                 | —                 | _           | _                 | _          | —          |                        |

|                   |                  | 15:8           | _                 | —                 | _                 | _           | _                 | —          | _          | —                      |

|                   |                  | 7:0            |                   |                   |                   |             | RH<23:16>         |            |            | T                      |

| 0x02D0            | U1BDTP3          | 31:24          |                   | —                 | —                 | —           | —                 | —          |            | -                      |

|                   |                  | 23:16          | _                 | —                 | —                 | —           | —                 | —          | _          |                        |

|                   |                  | 15:8           | —                 | —                 | —                 | —           | —                 | —          | _          | _                      |

|                   |                  | 7:0            |                   |                   |                   |             | RU<31:24>         |            |            | T                      |

| 0x02E0            | U1CNFG1          | 31:24          | _                 | —                 | —                 | —           | —                 | —          | _          |                        |

|                   |                  | 23:16          | —                 | —                 | —                 |             | —                 |            | _          |                        |

|                   |                  | 15:8           | —                 | —                 | —                 | —           | —                 |            | _          | —                      |

|                   |                  | 7:0            | UTEYE             | UOEMON            | USBFRZ            | USBSIDL     | —                 | —          | _          | UASUSPND <sup>(1</sup> |

| 0x0300            | U1EP0            | 31:24          | _                 | —                 | -                 | —           | —                 | —          | _          | —                      |

|                   |                  | 23:16          | _                 | —                 | -                 | —           | —                 | —          | _          | —                      |

|                   |                  | 15:8           | _                 | —                 | _                 | —           | —                 | —          | _          | —                      |

|                   |                  | 7:0            | LSPD              | RETRYDIS          | -                 | EPCONDIS    | EPRXEN            | EPTXEN     | EPSTALL    | EPHSHK                 |

| 0x0310            | U1EP1            | 31:24          | _                 | —                 | _                 | —           | —                 | _          | _          | —                      |

|                   |                  | 23:16          | _                 | —                 | _                 | —           | —                 | —          | _          | —                      |

|                   |                  | 15:8           | —                 | —                 | —                 | —           | —                 | —          | _          | —                      |

|                   |                  | 7:0            | —                 | —                 | —                 | EPCONDIS    | EPRXEN            | EPTXEN     | EPSTALL    | EPHSHK                 |

| 0x0320            | U1EP2            | 31:24          | —                 | —                 | —                 | —           | —                 | _          | _          | —                      |

|                   |                  | 23:16          | —                 | _                 | —                 | —           | _                 | —          |            | —                      |

|                   |                  | 15:8           | _                 | —                 | —                 | _           | _                 | _          |            | —                      |

|                   |                  | 7:0            | _                 | —                 | _                 | EPCONDIS    | EPRXEN            | EPTXEN     | EPSTALL    | EPHSHK                 |

| 0x0330            | U1EP3            | 31:24          | _                 | —                 | —                 | —           | —                 | _          | _          | -                      |

|                   |                  | 23:16          | —                 | —                 | —                 | —           | —                 | _          | _          | -                      |

|                   |                  | 15:8           | _                 | —                 | _                 | —           | _                 | _          | _          | —                      |

|                   |                  | 7:0            | _                 | —                 | _                 | EPCONDIS    | EPRXEN            | EPTXEN     | EPSTALL    | EPHSHK                 |

| 0x0340            | U1EP4            | 31:24          | _                 | —                 | _                 | —           | -                 | —          | —          | -                      |

|                   |                  | 23:16          | _                 | —                 | _                 | —           | —                 | —          | _          | -                      |

|                   |                  | 15:8           | _                 | _                 | _                 | _           | _                 | _          | _          | -                      |

|                   |                  | 7:0            | _                 | —                 | _                 | EPCONDIS    | EPRXEN            | EPTXEN     | EPSTALL    | EPHSHK                 |

#### Table 27-1: USB Register Summary (Continued)

Legend:

- = unimplemented, read as '0'. Address offset values are shown in hexadecimal.

**Note** 1: This bit is not available on all devices. Refer to the specific device data sheet for details.

| Address<br>Offset | Register<br>Name | Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-------------------|------------------|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 0x0350            | U1EP5            | 31:24        | _                 | —                 | —                 | _                 | _                 | —                 | _                | —                |

|                   |                  | 23:16        | —                 | —                 | —                 | —                 |                   | —                 | —                | —                |

|                   |                  | 15:8         | —                 | —                 | —                 | —                 |                   | —                 | —                | —                |

|                   |                  | 7:0          | —                 | —                 | —                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

| x0360             | U1EP6            | 31:24        | —                 | —                 | —                 | —                 | -                 | —                 | —                |                  |

|                   |                  | 23:16        | —                 | —                 | —                 | —                 | -                 | —                 | —                | _                |

|                   |                  | 15:8         | _                 | —                 | —                 | —                 |                   | -                 | —                | _                |

|                   |                  | 7:0          | —                 | —                 | —                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

| 0x0370            | U1EP7            | 31:24        | _                 | _                 | _                 | —                 | -                 | _                 | _                | _                |

|                   |                  | 23:16        | _                 | —                 | —                 | —                 |                   | -                 | —                | _                |

|                   |                  | 15:8         | —                 | —                 | —                 | —                 |                   | —                 | —                |                  |

|                   |                  | 7:0          | —                 | —                 | —                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

| 0x0380            | U1EP8            | 31:24        | —                 | —                 | —                 | —                 |                   | —                 | —                | _                |

|                   |                  | 23:16        | —                 | —                 | —                 | —                 |                   | —                 | —                |                  |

|                   |                  | 15:8         | —                 | —                 | —                 | —                 |                   | —                 | —                |                  |

|                   |                  | 7:0          | —                 | —                 | —                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

| 0x0390            | U1EP9            | 31:24        | —                 | —                 | —                 | —                 | -                 | —                 | —                |                  |

|                   |                  | 23:16        | —                 | —                 | —                 | —                 |                   | —                 | —                |                  |

|                   |                  | 15:8         | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

|                   |                  | 7:0          | _                 | —                 | —                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

| 0x03A0            | U1EP10           | 31:24        | _                 | —                 | —                 | —                 | -                 | _                 |                  | —                |

|                   |                  | 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

|                   |                  | 15:8         | _                 | —                 | —                 | —                 | _                 | _                 |                  | —                |

|                   |                  | 7:0          | —                 | —                 | —                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

| 0x03B0            | U1EP11           | 31:24        | —                 | —                 | —                 | —                 |                   | —                 | —                | _                |

|                   |                  | 23:16        | —                 | —                 | —                 | —                 |                   | —                 | —                |                  |

|                   |                  | 15:8         | —                 | —                 | —                 | —                 |                   | —                 | —                |                  |

|                   |                  | 7:0          | —                 | —                 | —                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

| 0x03C0            | U1EP12           | 31:24        | —                 | —                 | —                 | —                 | -                 | —                 | —                |                  |

|                   |                  | 23:16        | —                 | —                 | —                 | —                 |                   | —                 | —                |                  |

|                   |                  | 15:8         | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

|                   |                  | 7:0          | —                 | —                 | —                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

| x03D0             | U1EP13           | 31:24        | —                 | —                 | —                 | —                 | -                 | —                 | —                |                  |

|                   |                  | 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

|                   |                  | 15:8         | —                 | —                 | —                 | —                 |                   | —                 | —                | —                |

|                   |                  | 7:0          | —                 | —                 | —                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

| x03E0             | U1EP14           | 31:24        | —                 | —                 | —                 | —                 | _                 | —                 | —                | —                |

|                   |                  | 23:16        | _                 | —                 | —                 | —                 | —                 | _                 | —                | _                |

|                   |                  | 15:8         | _                 | —                 | —                 | —                 | —                 | —                 | _                | _                |

|                   |                  | 7:0          | _                 | —                 | _                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

| 0x03F0            | U1EP15           | 31:24        | _                 | _                 | _                 | —                 | —                 | _                 | —                | _                |

|                   |                  | 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|                   |                  | 15:8         | _                 | —                 | —                 | —                 | _                 | _                 | _                | _                |

|                   |                  | 7:0          | _                 | _                 | _                 | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

Table 27-1:

USB Register Summary (Continued)

Legend: — = unimplemented, read as '0'. Address offset values are shown in hexadecimal.

**Note** 1: This bit is not available on all devices. Refer to the specific device data sheet for details.

Refer to **Section 6. "Oscillators"** (DS61112) for information on the register bits used to enable the USB PLL and/or USB FRC clock sources.

Refer to **Section 8. "Interrupts"** (DS61108) for information on the register bits used to enable and identify the USB module interrupts.

Refer to **Section 32. "Configuration"** (DS61124) for information on the configuration bits used to enable the USB PLL and set the appropriate divisor. This section also describes the bits that can be used to reclaim the USBID and VBUSON pins if the USB module will only be operated in a mode that does not require them.

| r-x            | -1: U1OTGIR:<br>r-x                                                                                                                            | USB OTG Inte                                                                                                                          | r-x                                                                                                                                                   | r-x                                                               | r-x               | r-x          | r-x      |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-------------------|--------------|----------|

| _              | —                                                                                                                                              | _                                                                                                                                     | _                                                                                                                                                     | _                                                                 | _                 | _            | —        |

| bit 31         |                                                                                                                                                |                                                                                                                                       |                                                                                                                                                       |                                                                   |                   |              | bit 24   |

|                |                                                                                                                                                |                                                                                                                                       |                                                                                                                                                       |                                                                   |                   |              |          |

| r-x            | r-x                                                                                                                                            | r-x                                                                                                                                   | r-x                                                                                                                                                   | r-x                                                               | r-x               | r-x          | r-x      |

| _              | —                                                                                                                                              |                                                                                                                                       |                                                                                                                                                       |                                                                   | —                 | _            | —        |

| bit 23         |                                                                                                                                                |                                                                                                                                       |                                                                                                                                                       |                                                                   |                   |              | bit 16   |

|                |                                                                                                                                                |                                                                                                                                       |                                                                                                                                                       |                                                                   |                   |              |          |

| r-x            | r-x                                                                                                                                            | r-x                                                                                                                                   | r-x                                                                                                                                                   | r-x                                                               | r-x               | r-x          | r-x      |

| <br>bit 15     |                                                                                                                                                | _                                                                                                                                     |                                                                                                                                                       | _                                                                 | _                 |              | bit 8    |

| 511 15         |                                                                                                                                                |                                                                                                                                       |                                                                                                                                                       |                                                                   |                   |              | bit t    |

| R/W/K-0        | R/W/K-0                                                                                                                                        | R/W/K-0                                                                                                                               | R/W/K-0                                                                                                                                               | R/W/K-0                                                           | R/W/K-0           | r-x          | R/W/K-0  |

| IDIF           | T1MSECIF                                                                                                                                       | LSTATEIF                                                                                                                              | ACTVIF                                                                                                                                                | SESVDIF                                                           | SESENDIF          | _            | VBUSVDIF |

| bit 7          |                                                                                                                                                |                                                                                                                                       |                                                                                                                                                       |                                                                   |                   |              | bit (    |

|                |                                                                                                                                                |                                                                                                                                       |                                                                                                                                                       |                                                                   |                   |              |          |

| Legend:        |                                                                                                                                                |                                                                                                                                       |                                                                                                                                                       |                                                                   |                   |              |          |

| R = Readab     | ole bit                                                                                                                                        | W = Writable                                                                                                                          | bit                                                                                                                                                   | P = Programn                                                      | nable bit         | r = Reserve  | d bit    |

| U = Unimple    | emented bit                                                                                                                                    | K = Write '1' t                                                                                                                       | o clear                                                                                                                                               | -n = Bit Value                                                    | at POR: ('0', '1' | , x = unknov | wn)      |

| bit 31-8       | Reserved: W                                                                                                                                    | /rite '0'; ignore i                                                                                                                   | ead                                                                                                                                                   |                                                                   |                   |              |          |

| bit 7          |                                                                                                                                                | Change Indica                                                                                                                         |                                                                                                                                                       |                                                                   |                   |              |          |

|                |                                                                                                                                                | this bit to clear                                                                                                                     |                                                                                                                                                       |                                                                   |                   |              |          |

|                | 1 = Change i                                                                                                                                   | in ID state dete                                                                                                                      | cted                                                                                                                                                  |                                                                   |                   |              |          |

| 1.10           |                                                                                                                                                | ge in ID state d                                                                                                                      |                                                                                                                                                       |                                                                   |                   |              |          |

| bit 6          |                                                                                                                                                | Millisecond Til<br>this bit to clear                                                                                                  |                                                                                                                                                       |                                                                   |                   |              |          |

|                |                                                                                                                                                | cond timer has                                                                                                                        |                                                                                                                                                       |                                                                   |                   |              |          |

|                | 0 = 1 millised                                                                                                                                 | cond timer has                                                                                                                        | not expired                                                                                                                                           |                                                                   |                   |              |          |

| bit 5          | LSTATEIF: L                                                                                                                                    | ine State Stable                                                                                                                      | Indicator bit                                                                                                                                         |                                                                   |                   |              |          |

|                |                                                                                                                                                | this bit to clear                                                                                                                     |                                                                                                                                                       | - but different                                                   |                   |              |          |

|                |                                                                                                                                                | state has been                                                                                                                        |                                                                                                                                                       | s, but different                                                  | from last time    |              |          |

| bit 4          |                                                                                                                                                | Activity Indicat                                                                                                                      |                                                                                                                                                       |                                                                   |                   |              |          |

|                |                                                                                                                                                | this bit to clear                                                                                                                     |                                                                                                                                                       |                                                                   |                   |              |          |

|                | •                                                                                                                                              |                                                                                                                                       |                                                                                                                                                       | has caused the                                                    | e device to wake  | e-up         |          |

| L:1 0          | -                                                                                                                                              | as not been de                                                                                                                        |                                                                                                                                                       | L.11                                                              |                   |              |          |

| nit K          |                                                                                                                                                | ession Valid Cha                                                                                                                      | •                                                                                                                                                     | DIT                                                               |                   |              |          |

| DIL J          | M/rito o '1' to '                                                                                                                              |                                                                                                                                       |                                                                                                                                                       |                                                                   |                   |              |          |

| DIL O          |                                                                                                                                                | tage has dropp                                                                                                                        | ed below the s                                                                                                                                        | ession end leve                                                   |                   |              |          |

|                | 1 = VBUS vol<br>0 = VBUS vol                                                                                                                   | tage has dropp<br>tage has not dr                                                                                                     | ed below the s<br>opped below th                                                                                                                      | he session end                                                    |                   |              |          |

| bit 3<br>bit 2 | 1 = VBUS vol<br>0 = VBUS vol<br><b>SESENDIF:</b> B                                                                                             | tage has dropp<br>tage has not dr<br>3-Device Vвus                                                                                    | ed below the s<br>opped below tl<br>Change Indica                                                                                                     | he session end                                                    |                   |              |          |

|                | 1 = VBUS vol<br>0 = VBUS vol<br><b>SESENDIF:</b> B<br>Write a '1' to                                                                           | tage has dropp<br>tage has not dr<br>3-Device VBUS<br>this bit to clear                                                               | ed below the s<br>opped below tl<br>Change Indica<br>the interrupt.                                                                                   | he session end<br>tor bit                                         |                   |              |          |

|                | 1 = VBUS vol<br>0 = VBUS vol<br>SESENDIF: F<br>Write a '1' to<br>1 = A change                                                                  | tage has dropp<br>tage has not dr<br>3-Device Vвus                                                                                    | ed below the s<br>opped below th<br>Change Indica<br>the interrupt.<br>n end input wa                                                                 | he session end<br>tor bit<br>s detected                           |                   |              |          |

| bit 2          | 1 = VBUS vol<br>0 = VBUS vol<br><b>SESENDIF:</b> E<br>Write a '1' to<br>1 = A change<br>0 = No change                                          | tage has dropp<br>tage has not dr<br>3-Device VBUS<br>this bit to clear<br>e on the session                                           | ed below the s<br>opped below the<br>Change Indica<br>the interrupt.<br>n end input wa<br>on end input wa                                             | he session end<br>tor bit<br>s detected                           |                   |              |          |

| bit 2<br>bit 1 | 1 = VBUS vol<br>0 = VBUS vol<br>SESENDIF: E<br>Write a '1' to<br>1 = A change<br>0 = No change<br>Reserved: W                                  | tage has dropp<br>tage has not dr<br>3-Device VBUS<br>this bit to clear<br>e on the session<br>ge on the session                      | ed below the s<br>opped below the<br>Change Indica<br>the interrupt.<br>n end input wa<br>on end input w<br>read                                      | he session end<br>tor bit<br>s detected<br>as detected            |                   |              |          |

|                | 1 = VBUS vol<br>0 = VBUS vol<br>SESENDIF: E<br>Write a '1' to<br>1 = A change<br>0 = No change<br>Reserved: W<br>VBUSVDIF: A<br>Write a '1' to | tage has dropp<br>tage has not dr<br>3-Device VBUS<br>this bit to clear<br>e on the session<br>ge on the session<br>ge on the session | ed below the s<br>opped below the<br>Change Indica<br>the interrupt.<br>In end input wa<br>on end input wa<br>read<br>Change Indica<br>the interrupt. | he session end<br>tor bit<br>s detected<br>as detected<br>tor bit |                   |              |          |

| r-x                                                                           | r-x                                                                                                                                                                                                                                                                                                                                                                             | r-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | r-x                                                                                                                                                                                                             | r-x                                 | r-x       | r-x         | r-x      |

|-------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|-----------|-------------|----------|

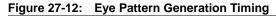

| _                                                                             | —                                                                                                                                                                                                                                                                                                                                                                               | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                                                                                                                                                                                                               | —                                   | —         |             | —        |