# Section 19. Comparator

# HIGHLIGHTS

This section of the manual contains the following topics:

| 19.1 | Introduction                              |  |

|------|-------------------------------------------|--|

| 19.2 | Comparator Control Registers              |  |

| 19.3 | Comparator Operation                      |  |

| 19.4 | Interrupts                                |  |

| 19.5 | I/O Pin Control                           |  |

| 19.6 | Operation in Power-Saving and Debug Modes |  |

| 19.7 | Effects of a Reset                        |  |

| 19.8 | Related Application Notes                 |  |

| 19.9 | Revision History                          |  |

# 19.1 INTRODUCTION

The PIC32MX Analog Comparator module contains one or more comparator(s) that can be configured in a variety of ways.

Following are some of the key features of this module:

- Selectable inputs available include:

- Analog inputs multiplexed with I/O pins

- On-Chip Internal Absolute Voltage Reference (IVREF)

- Comparator Voltage Reference (CVREF)

- Outputs can be inverted

- Selectable interrupt generation

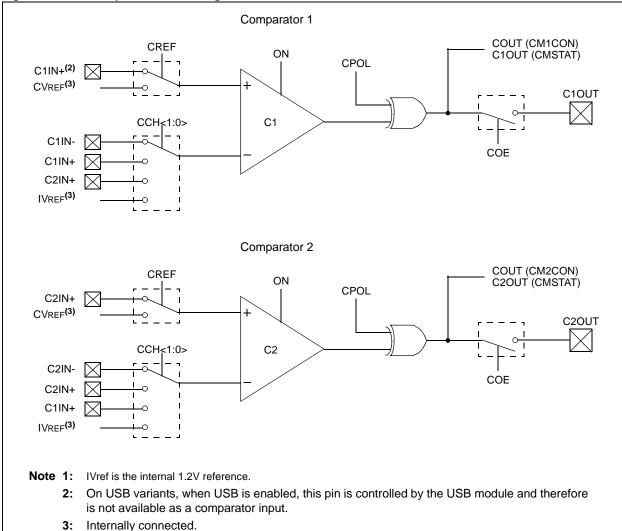

A block diagram of the comparator module is shown in Figure 19-1.

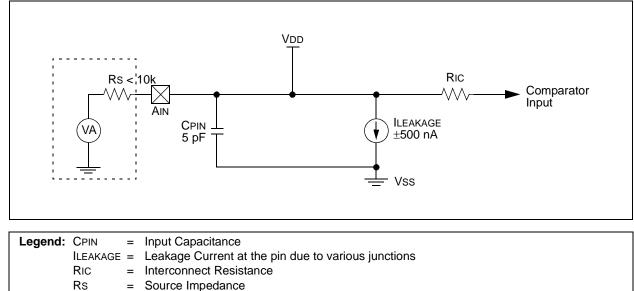

Figure 19-1: Comparator Block Diagram

# 19.2 COMPARATOR CONTROL REGISTERS

**Note:** Each PIC32MX device variant may have one or more Comparator modules. An 'x' used in the names of pins, control/Status bits and registers denotes the particular module. Refer to the specific device data sheets for more details.

A Comparator module consists of the following Special Function Registers (SFRs):

- CMxCON: Comparator Control Register for Module 'x'

- CMxCONCLR, CMxCONSET, CMxCONINV: Atomic Bit Write-only Manipulation Registers for CMxCON

- CMSTAT: Comparator Status Register

- CMSTATCLR, CMSTATSET, CMSTATINV: Atomic Bit Write-only Manipulation Registers for CMSTAT

The Comparator module also has the following interrupt control registers:

- IFS1: Interrupt Flag Status Register

- IFS1CLR, IFS1SET, IFS1INV: Atomic Bit Manipulation Write-only Registers for IFS1

- IEC1: Interrupt Enable Control Register

- IEC1CLR, IEC1SET, IEC1INV: Atomic Bit Manipulation Write-only Registers for IEC1

- IPC7: Interrupt Priority Control Register

- IPC7CLR, IPC7SET, IPC7INV: Atomic Bit Write-only Manipulation Registers for IPC7

The following table provides a brief summary of all Comparator-related registers. Corresponding registers appear after the summary, followed by a detailed description of each register.

| Name      | -     | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

|           |       | 31/23/13/1        | 30/22/14/0        | 23/21/13/3        | 20/20/12/4        | 2//13/11/3        | 20/10/10/2        | 23/17/9/1        | 24/10/0/0        |

| CM1CON    | 31:24 |                   | _                 |                   | —                 | —                 | _                 | —                | —                |

|           | 23:16 | _                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

|           | 15:8  | ON                | COE               | CPOL              | —                 | —                 | -                 | —                | COUT             |

|           | 7:0   | EVPO              | L<1:0>            | _                 | CREF              | —                 | _                 | CCH              | <1:0>            |

| CM1CONCLR | 31:0  |                   | Write             | clears selecte    | d bits in CM1     | CON, read yie     | lds undefined     | l value          |                  |

| CM1CONSET | 31:0  |                   | Write             | sets selected     | I bits in CM1C    | ON, read yiel     | ds undefined      | value            |                  |

| CM1CONINV | 31:0  |                   | Write i           | nverts selecte    | ed bits in CM1    | CON, read yie     | elds undefined    | d value          |                  |

| CM2CON    | 31:24 | _                 | _                 | —                 | —                 | —                 |                   | —                | —                |

|           | 23:16 | -                 | _                 | -                 | —                 | —                 | _                 | —                | —                |

|           | 15:8  | ON                | COE               | CPOL              | —                 | —                 | _                 | —                | COUT             |

|           | 7:0   | EVPO              | L<1:0>            | -                 | CREF              | —                 | _                 | CCH              | <1:0>            |

| CM2CONCLR | 31:0  |                   | Write             | clears selecte    | d bits in CM2     | CON, read yie     | elds undefined    | l value          |                  |

| CM2CONSET | 31:0  |                   | Write             | sets selected     | I bits in CM2C    | ON, read yiel     | ds undefined      | value            |                  |

| CM2CONINV | 31:0  |                   | Write i           | nverts selecte    | ed bits in CM2    | CON, read yie     | elds undefined    | d value          |                  |

| CMSTAT    | 31:24 | _                 | _                 | —                 | —                 | —                 |                   | —                | —                |

|           | 23:16 | _                 | _                 | _                 | —                 | —                 | _                 | —                | —                |

|           | 15:8  | _                 | FRZ               | SIDL              | —                 | —                 | _                 | —                | —                |

|           | 7:0   | _                 | _                 | _                 | —                 | —                 | _                 | C2OUT            | C1OUT            |

| CMSTATCLR | 31:0  |                   | Write             | clears selecte    | ed bits in CMS    | STAT, read yie    | lds undefined     | value            |                  |

| CMSTATSET | 31:0  |                   | Write             | e sets selecte    | d bits in CMS     | TAT, read yield   | ds undefined v    | value            |                  |

| CMSTATINV | 31:0  |                   | Write             | inverts selecte   | ed bits in CMS    | STAT, read yie    | lds undefined     | lvalue           |                  |

Table 19-1: Comparator SFRs Summary

Comparator

| Name    |       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|---------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| IFS1    | 31:24 | _                 | _                 | _                 | _                 | —                 | _                 | USBIF            | FCEIF            |

|         | 23:16 | _                 | _                 | _                 | _                 | DMA3IF            | DMA2IF            | DMA1IF           | DMA0IF           |

|         | 15:8  | RTCCIF            | FSCMIF            | I2C2MIF           | I2C2SIF           | I2C2BIF           | U2TXIF            | U2RXIF           | U2EIF            |

|         | 7:0   | SPI2RXIF          | SPI2TXIF          | SPI2EIF           | CMP2IF            | CMP1IF            | PMPIF             | AD1IF            | CNIF             |

| IFS1CLR | 31:0  |                   | Cle               | ears the select   | ted bits in IFS   | 1, read yields    | undefined va      | lue              |                  |

| IFS1SET | 31:0  |                   | Se                | ets the selecte   | ed bits in IFS1   | , read yields u   | undefined valu    | le               |                  |

| IFS1INV | 31:0  |                   | Inv               | erts the selec    | ted bits in IFS   | 1, read yields    | undefined va      | lue              |                  |

| IEC1    | 31:24 |                   |                   |                   |                   | —                 |                   | USBIE            | FCEIE            |

|         | 23:16 |                   |                   |                   |                   | DMA3IE            | DMA2IE            | DMA1IE           | DMA0IE           |

|         | 15:8  | RTCCIE            | FSCMIE            | I2C2MIE           | I2C2SIE           | I2C2BIE           | U2TXIE            | U2RXIE           | U2EIE            |

|         | 7:0   | SPI2RXIE          | SPI2TXIE          | SPI2EIE           | CMP2IE            | CMP1IE            | PMPIE             | AD1IE            | CNIE             |

| IEC1CLR | 31:0  |                   | Cle               | ars the select    | ted bits in IEC   | 1, read yields    | undefined va      | lue              |                  |

| IEC1SET | 31:0  |                   | Se                | ets the selecte   | ed bits in IEC1   | l, read yields    | undefined value   | ue               |                  |

| IEC1INV | 31:0  |                   |                   | Inverts the se    | lected bits in I  | EC1, read yie     | lds undefined     | l                |                  |

| IPC7    | 31:24 | -                 | _                 | _                 |                   | SPI2IP<2:0>       |                   | SP2IS            | <1:0>            |

|         | 23:16 | -                 | _                 | _                 |                   | CMP2IP<2:0>       | •                 | CMP2I            | S<1:0>           |

|         | 15:8  | _                 | _                 | _                 |                   | CMP1IP<2:0>       | •                 | CMP1I            | S<1:0>           |

|         | 7:0   | —                 | —                 | —                 |                   | PMPIP<2:0>        |                   | PMPIS            | S<1:0>           |

| IPC7CLR | 31:0  |                   | Cle               | ears the select   | ted bits in IPC   | 7, read yields    | undefined va      | lue              |                  |

| IPC7SET | 31:0  |                   | Se                | ets the selecte   | ed bits in IPC7   | , read yields     | undefined val     | ue               |                  |

| IPC7INV | 31:0  |                   | Inv               | erts the select   | ted bits in IPC   | 7, read yields    | undefined va      | llue             |                  |

# Table 19-1: Comparator SFRs Summary (Continued)

| r-x                                                          | r-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | r-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | r-x                                                                                                                                                                                                                                                                                                                        | r-x                                                                                                                                                                                             | r-x                                                                                                                                                                                            | r-x                               | r-x                                                                 |  |  |  |  |

|--------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|---------------------------------------------------------------------|--|--|--|--|

| _                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                               |                                                                                                                                                                                                | _                                 | _                                                                   |  |  |  |  |

| it 31                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                 |                                                                                                                                                                                                |                                   | bit 24                                                              |  |  |  |  |

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                 |                                                                                                                                                                                                |                                   |                                                                     |  |  |  |  |

| r-x                                                          | r-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | r-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | r-x                                                                                                                                                                                                                                                                                                                        | r-x                                                                                                                                                                                             | r-x                                                                                                                                                                                            | r-x                               | r-x                                                                 |  |  |  |  |

| —                                                            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                                                          | —                                                                                                                                                                                               | —                                                                                                                                                                                              |                                   | —                                                                   |  |  |  |  |

| it 23                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                 |                                                                                                                                                                                                |                                   | bit 1                                                               |  |  |  |  |

| R/W-0                                                        | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | r-x                                                                                                                                                                                                                                                                                                                        | r-x                                                                                                                                                                                             | r-x                                                                                                                                                                                            | r-x                               | R-0                                                                 |  |  |  |  |

| ON                                                           | COE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CPOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                          | _                                                                                                                                                                                               | _                                                                                                                                                                                              |                                   | COUT                                                                |  |  |  |  |

| it 15                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0.01                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                 |                                                                                                                                                                                                |                                   | bit                                                                 |  |  |  |  |

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                 |                                                                                                                                                                                                |                                   |                                                                     |  |  |  |  |

| R/W-1                                                        | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | r-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0                                                                                                                                                                                                                                                                                                                      | r-x                                                                                                                                                                                             | r-x                                                                                                                                                                                            | R/W-1                             | R/W-1                                                               |  |  |  |  |

| EVP                                                          | OL<1:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | CREF                                                                                                                                                                                                                                                                                                                       | —                                                                                                                                                                                               | _                                                                                                                                                                                              | CCH                               | l<1:0>                                                              |  |  |  |  |

| it 7                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                 |                                                                                                                                                                                                |                                   | bit                                                                 |  |  |  |  |

|                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                 |                                                                                                                                                                                                |                                   |                                                                     |  |  |  |  |