# Section 13. Parallel Master Port (PMP)

# HIGHLIGHTS

This section of the manual contains the following topics:

| 13.1  | Introduction                              |  |

|-------|-------------------------------------------|--|

| 13.2  | Control Registers                         |  |

| 13.3  | Master Modes of Operation                 |  |

| 13.4  | Slave Modes of Operation                  |  |

| 13.5  | Interrupts                                |  |

| 13.6  | Operation in Power-Saving and Debug Modes |  |

| 13.7  | Effects of Various Resets                 |  |

| 13.8  | Parallel Master Port Applications         |  |

| 13.9  | Parallel Slave Port Application           |  |

| 13.10 | I/O Pin Control                           |  |

| 13.11 | Design Tips                               |  |

| 13.12 | Related Application Notes                 |  |

| 13.13 | Revision History                          |  |

13

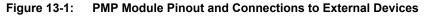

### 13.1 INTRODUCTION

The Parallel Master Port (PMP) is a parallel 8-bit/16-bit I/O module specifically designed to communicate with a wide variety of parallel devices such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interfaces to parallel peripherals vary significantly, the PMP module is highly configurable.

Key features of the PMP module include:

- · Up to 16 programmable address lines

- · Up to two Chip Select lines

- Programmable strobe options

- Individual read and write strobes, or

- Read/write strobe with enable strobe

- Address auto-increment/auto-decrement

- Programmable address/data multiplexing

- · Programmable polarity on control signals

- · Legacy parallel slave port support

- Enhanced parallel slave support

- Address support

- 4-bytes-deep, auto-incrementing buffer

- · Schmitt Trigger or TTL input buffers

- Programmable Wait states

- · Freeze option for in-circuit debugging

## 13.2 CONTROL REGISTERS

The PMP module uses these Special Function Registers (SFRs):

#### PMCON: Parallel Port Control Register

This register (Register 13-1) contains the bits that control much of the module's basic functionality. A key bit is the ON control bit, which is used to Reset, enable or disable the module.

When the module is disabled, all of the associated I/O pins revert to their designated I/O function. In addition, any read or write operations active or pending are stopped, and the BUSY bit is cleared. The data within the module registers is retained, including the data in PMSTAT register. Therefore, the module could be disabled after a reception, and the last received data and status would still be available for processing.

When the module is enabled, all buffer control logic is reset, along with PMSTAT.

All other bits in PMCON control address multiplexing, enable various port control signals, and select control signal polarity. These are discussed in more detail in **13.3.1** "**Parallel Master Port Configuration Options**".

#### PMMODE: Parallel Port Mode Register

This register (Register 13-2) contains bits that control the operational modes of the module. Master/Slave mode selection, as well as configuration options for both modes, are set by this register. It also contains the universal status flag BUSY, used in Master modes to indicate that an operation by the module in progress.

Details on the use of the PMMODE bits to configure PMP operation are provided in **13.4 "Slave Modes of Operation"** and **13.3 "Master Modes of Operation"**.

#### • PMADDR: Parallel Port Address Register

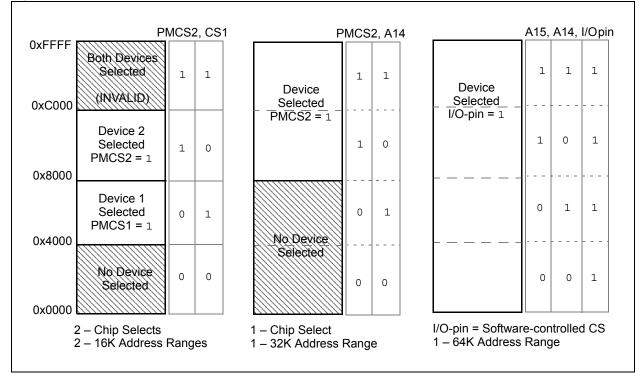

This register (Register 13-3) functions as PMADDR in master modes. It contains the address to which outgoing data is to be written, as well as the Chip Select control bits for addressing parallel slave devices. The PMADDR register is not used in any of the Slave modes.

#### PMDOUT: Parallel Port Data Output Register

This register (Register 13-4) is only used in Slave mode for buffered output data.

#### PMDIN: Parallel Port Data Input Register

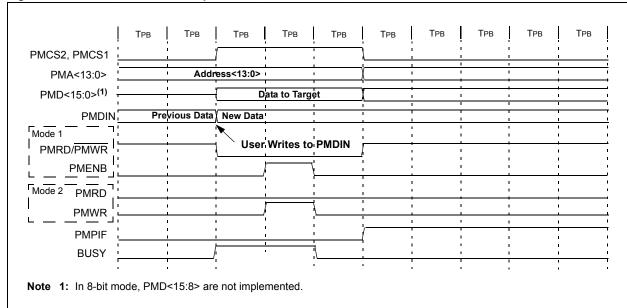

This register (Register 13-5) is used by the PMP module in both Master and Slave modes.

In Slave mode, this register is used to hold data that is asynchronously clocked in. Its operation is described in **13.4.2 "Buffered Parallel Slave Port Mode"**.

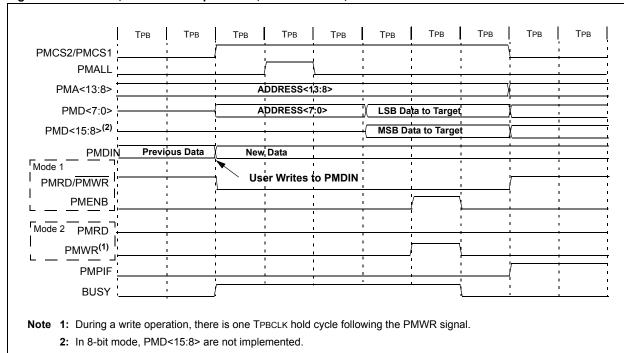

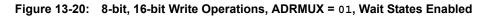

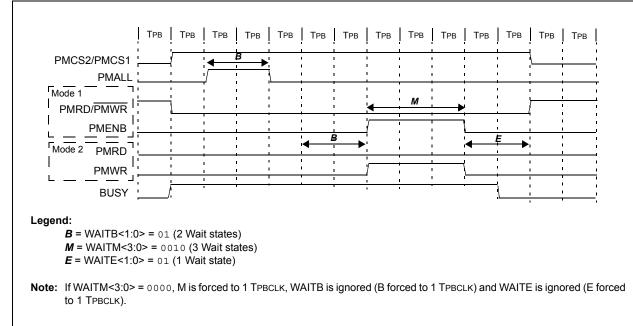

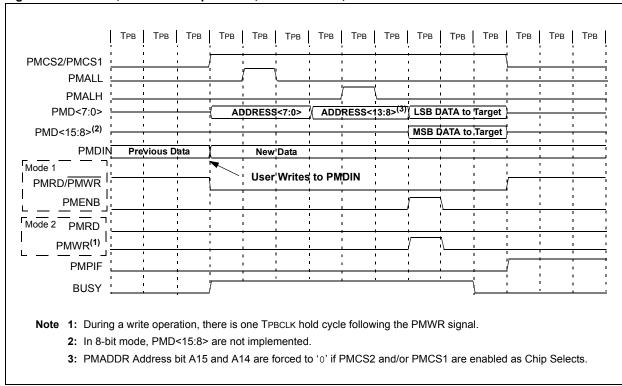

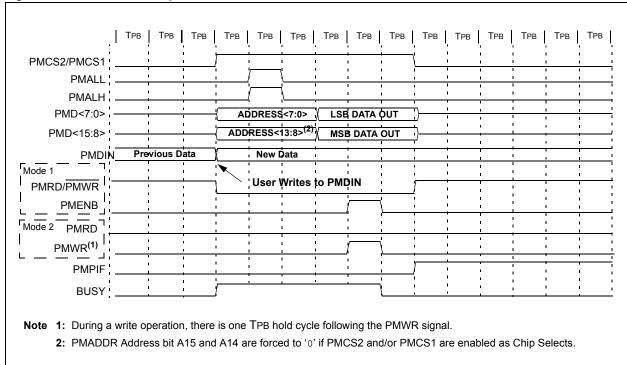

In Master mode, PMDIN is the holding register for both incoming and outgoing data. Its operation in Master mode is described in **13.3.3 "Read Operation"** and **13.3.4 "Write Operation"**.

#### PMAEN: Parallel Port Pin Enable Register

This register (Register 13-6) controls the operation of address and Chip Select pins associated to this module. Setting these bits allocates the corresponding microcontroller pins to the PMP module; clearing the bits allocates the pins to port I/O or other peripheral modules associated with the pin.

#### PMSTAT: Parallel Port Status Register (Slave modes only)

This register (Register 13-7) contains Status bits associated with buffered operating modes when the port is functioning as a Slave port. This includes overflow, underflow and full flag bit.

These flags are discussed in detail in 13.4.2 "Buffered Parallel Slave Port Mode".

### 13.2.1 PMP SFR Summary

Table 13-1 provides a brief summary of all PMP-module-related registers. Corresponding registers appear after the summary with a detailed description of each bit.

| Table 13-         | 1: PMP SFI                | ( Ouiii |                   |                   |                   |                   |                   |                   |                  |                  |

|-------------------|---------------------------|---------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Address<br>Offset | Name                      |         | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|                   | PMCON <sup>(1,2,3)</sup>  | 31:24   |                   | -                 |                   | —                 | —                 | —                 |                  | —                |

|                   |                           | 23:16   | —                 | -                 | _                 | —                 | —                 | —                 | _                | —                |

|                   |                           | 15:8    | ON                | FRZ               | SIDL              | ADRMU             | JX<1:0>           | PMPTTL            | PTWREN           | PTRDEN           |

|                   |                           | 7:0     | CSF∢              | <1:0>             | ALP               | CS2P              | CS1P              | —                 | WRSP             | RDSP             |

|                   | PMMODE <sup>(1,2,3)</sup> | 31:24   | _                 | —                 | _                 | —                 | —                 | —                 | -                | —                |

|                   |                           | 23:16   |                   |                   | _                 |                   | —                 | _                 |                  |                  |

|                   |                           | 15:8    | BUSY              | IRQM              | <1:0>             | INCM              | <1:0>             | MODE16            | MODE             | <1:0>            |

|                   |                           | 7:0     | WAITE             | 3<1:0>            |                   | WAITN             | /<3:0>            |                   | WAITE            | <1:0>            |

|                   | PMADDR <sup>(1,2,3)</sup> | 31:24   |                   |                   | _                 |                   | —                 |                   |                  |                  |

|                   |                           | 23:16   |                   | _                 | —                 | —                 | —                 | —                 |                  | —                |

|                   |                           | 15:8    | CS2/A15           | CS1/A14           |                   |                   | ADDR              | <13:8>            |                  |                  |

|                   |                           | 7:0     |                   |                   |                   | ADDR              | <7:0>             |                   |                  |                  |

|                   | PMDOUT <sup>(1,2,3)</sup> | 31:24   |                   |                   |                   | DATAOU            | T<31:24>          |                   |                  |                  |

|                   |                           | 23:16   |                   |                   |                   | DATAOU            | T<23:16>          |                   |                  |                  |

|                   |                           | 15:8    |                   |                   |                   | DATAOU            | IT<15:8>          |                   |                  |                  |

|                   |                           | 7:0     |                   |                   |                   | DATAOL            | JT<7:0>           |                   |                  |                  |

|                   | PMDIN <sup>(1,2,3)</sup>  | 31:24   |                   |                   |                   | DATAIN            | <31:24>           |                   |                  |                  |

|                   |                           | 23:16   |                   |                   |                   | DATAIN            | <23:16>           |                   |                  |                  |

|                   |                           | 15:8    |                   |                   |                   | DATAIN            | l<15:8>           |                   |                  |                  |

|                   |                           | 7:0     |                   |                   |                   | DATAI             | N<7:0>            |                   |                  |                  |

|                   | PMAEN <sup>(1,2,3)</sup>  | 31:24   |                   |                   |                   |                   | —                 |                   |                  |                  |

|                   |                           | 23:16   | —                 | —                 | —                 | —                 | —                 | —                 | _                | —                |

|                   |                           | 15:8    |                   |                   |                   | PTEN•             | <15:8>            |                   |                  |                  |

|                   |                           | 7:0     |                   |                   |                   | PTEN              | <7:0>             |                   |                  |                  |

|                   | PMSTAT                    | 31:24   |                   |                   | —                 | _                 | —                 | —                 |                  | —                |

|                   |                           | 23:16   |                   | —                 | —                 | —                 | —                 | —                 | —                | —                |

|                   |                           | 15:8    | IBF               | IBOV              |                   | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

|                   |                           | 7:0     | OBE               | OBUF              |                   | —                 | OB3E              | OB2E              | OB1E             | OB0E             |

Table 13-1: PMP SFR Summary

**Legend:** — = unimplemented, read as '0'. Address offset values are shown in hexadecimal.

**Note** 1: This register has an associated Clear register at an offset of 0x4 bytes. These registers have the same name with CLR appended to the end of the register name (e.g., PMCONCLR). Writing a '1' to any bit position in the Clear register will clear valid bits in the associated register. Reads from the Clear register should be ignored.

2: This register has an associated Set register at an offset of 0x8 bytes. These registers have the same name with SET appended to the end of the register name (e.g., PMCONSET). Writing a '1' to any bit position in the Set register will set valid bits in the associated register. Reads from the Set register should be ignored.

3: This register has an associated Invert register at an offset of 0xC bytes. These registers have the same name with INV appended to the end of the register name (e.g., PMCONINV). Writing a '1' to any bit position in the Invert register will invert valid bits in the associated register. Reads from the Invert register should be ignored.

|                                        | r-x                                                                                                                                                                                                                                                                                                               | r-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | r-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | r-x                                                                                                                                                                                                                                                                 | r-x                                                                                                                                                                                                        | r-x                                                                                                                                                | r-x                                                                                                                           |

|----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|

|                                        | _                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                          |                                                                                                                                                    |                                                                                                                               |

| it 31                                  |                                                                                                                                                                                                                                                                                                                   | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                            |                                                                                                                                                    | bit 24                                                                                                                        |

|                                        |                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                            |                                                                                                                                                    |                                                                                                                               |

| r-x                                    | r-x                                                                                                                                                                                                                                                                                                               | r-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | r-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | r-x                                                                                                                                                                                                                                                                 | r-x                                                                                                                                                                                                        | r-x                                                                                                                                                | r-x                                                                                                                           |

| —                                      | —                                                                                                                                                                                                                                                                                                                 | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | —                                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                          | —                                                                                                                                                  | _                                                                                                                             |

| it 23                                  |                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                            |                                                                                                                                                    | bit 16                                                                                                                        |

| R/W-0                                  | R/W-0                                                                                                                                                                                                                                                                                                             | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0                                                                                                                                                                                                                                                               | R/W-0                                                                                                                                                                                                      | R/W-0                                                                                                                                              | R/W-0                                                                                                                         |

| ON                                     | FRZ                                                                                                                                                                                                                                                                                                               | SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | JX<1:0>                                                                                                                                                                                                                                                             | PMPTTL                                                                                                                                                                                                     | PTWREN                                                                                                                                             | PTRDEN                                                                                                                        |

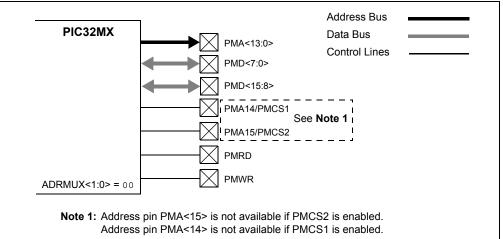

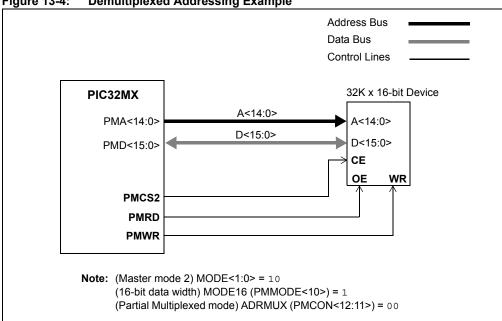

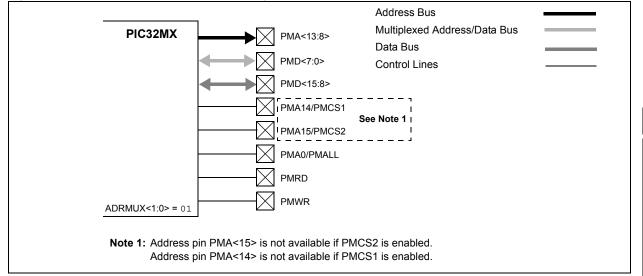

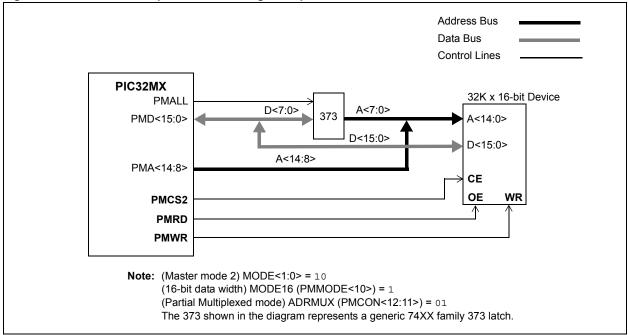

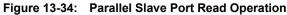

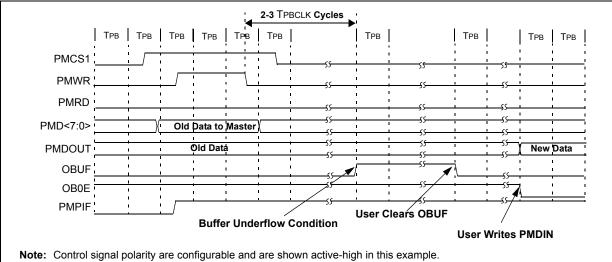

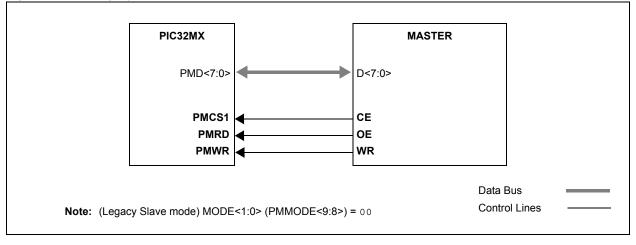

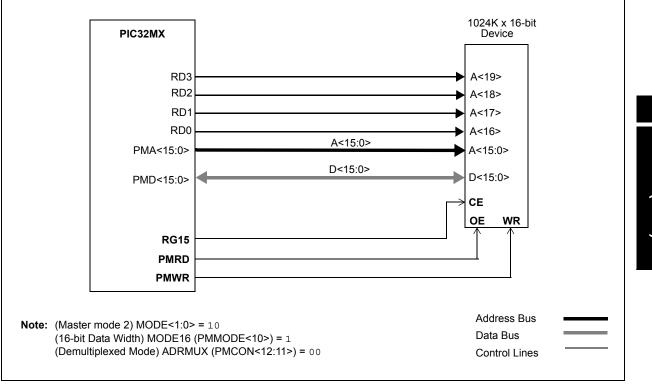

| it 15                                  | 1112                                                                                                                                                                                                                                                                                                              | OIDE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 7.01.00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 57(11.0)                                                                                                                                                                                                                                                            |                                                                                                                                                                                                            | 1 HWILLIN                                                                                                                                          | bit 8                                                                                                                         |