# **Section 4. Prefetch Cache Module**

# HIGHLIGHTS

This section of the manual contains the following topics:

| Introduction                    |                                                                                                                                                                                                        |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Cache Overview                  |                                                                                                                                                                                                        |

| Control Registers               | 4-7                                                                                                                                                                                                    |

| Cache Operation                 |                                                                                                                                                                                                        |

| Cache Configurations            |                                                                                                                                                                                                        |

| Coherency Support               |                                                                                                                                                                                                        |

| Effects of Reset                | 4-31                                                                                                                                                                                                   |

| Design Tips                     |                                                                                                                                                                                                        |

| Operation In Power-Saving Modes |                                                                                                                                                                                                        |

| Related Application Notes       |                                                                                                                                                                                                        |

| Revision History                | 4-34                                                                                                                                                                                                   |

|                                 | Cache Overview<br>Control Registers<br>Cache Operation<br>Cache Configurations<br>Coherency Support<br>Effects of Reset<br>Design Tips<br>Operation In Power-Saving Modes<br>Related Application Notes |

Pretetch Cache

# 4.1 INTRODUCTION

**Note:** Prefetch cache is available in select devices only. Refer to the appropriate data sheet for the availability of a prefetch cache module on specific devices.

This section describes the features and operation of the prefetch cache module in the PIC32MX device family. Prefetch cache features increase system performance for most applications.

PFM cache and prefetch cache modules increase performance for applications that execute out of the cacheable Program Flash Memory (PFM) region by implementing the following features:

Instruction Caching

The 16-line cache supplies an instruction every clock, for loops up to 256 bytes long.

• Data Caching

Prefetch cache also allows the allocation of up to 4 cache lines for data storage to provide improved access for Flash-stored constant data.

Predictive Prefetching

The prefetch cache module provides instructions once per clock for linear code even without caching by prefetching ahead of the current program counter, hiding the access time of the Flash memory.

## 4.1.1 Additional Prefetch Cache Module Features

The prefetch cache module also include the following features:

- 16 Fully Associative Lockable Cache Lines

- 16-Byte Cache Lines

- Up to 4 Cache Lines Allocated to Data

- 2 Cache Lines with Address Mask to Hold Repeated Instructions

- · Pseudo Least-Recently-Used (LRU) Replacement Policy

- All Cache Lines are Software Writable

- 16-Byte Parallel Memory Fetch

- Predictive Instruction Prefetch Cache

# 4.2 CACHE OVERVIEW

The prefetch cache module is a performance enhancing module included in some processors of the PIC32MX. When running at high clock rates, Wait states must be inserted into PFM Read transactions to meet the access time of the PFM. Wait states can be hidden to the core by prefetching and storing instructions in a temporary holding area that the CPU can access quickly. Although the data path to the CPU is 32-bits wide, the data path to the Program Memory Flash is 128-bits wide. This wide data path provides the same bandwidth to the CPU as a 32-bit path running at four times the frequency.

There are two main functions that the prefetch cache module performs: caching instructions when they are accessed, and prefetching instructions from the PFM before they are needed.

The cache holds a subset of the cacheable memory in temporary holding spaces known as cache lines. Each cache line has a tag describing what it is currently holding, and the address where it is mapped. Normally, the cache lines just hold a copy of what is currently in memory to make data available to the CPU without Wait states.

CPU requested data may or may not be in the cache. A cache-miss occurs if the CPU requests cacheable data that is not in the cache. In this case, a read is performed to the PFM at the correct address, the data is supplied to the cache and to the CPU. A cache-hit occurs if the cache contains the data that the CPU requests. In the case of a cache-hit, data is supplied to the CPU without Wait states.

The second main function of the prefetch cache module is to prefetch cache instructions. The module calculates the address of the next cache line and performs a read of the PFM to get the next 16-byte cache line. This line is placed into a 16-byte-wide prefetch cache buffer in anticipation of executing straight-line code.

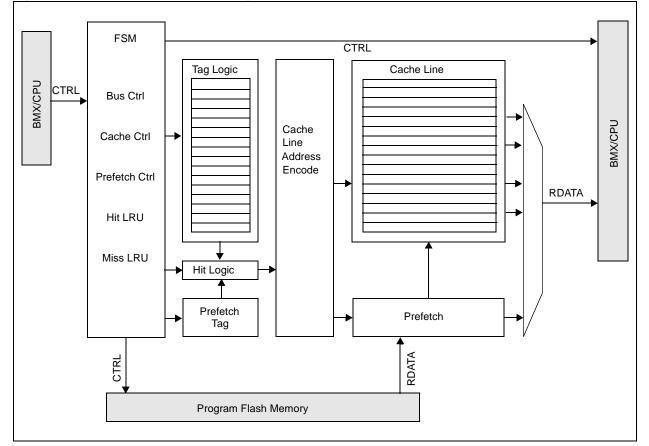

Figure 4-1 shows a block diagram of the prefetch cache module. Logically, the prefetch cache module fits between the Bus Matrix (BMX) module and the PFM module.

Figure 4-1: Prefetch Cache Block Diagram

To illustrate the basic operation of the prefetch cache, Figure 4-2 shows an example of the CPU requesting data from physical address 0x1FC01234. The prefetch cache simultaneously compares this address to all of the tags marked "valid". Since the shaded entry below has this address, and is marked as valid, this is a cache hit. The proper data word from the data array is then directed to the CPU in a single clock period.

| gure 4-2: | Cache Look-up Example <sup>(2)</sup> |        |        |         |        |

|-----------|--------------------------------------|--------|--------|---------|--------|

|           |                                      |        |        |         |        |

|           |                                      |        |        |         |        |

|           | ~                                    |        | ^      |         |        |

|           | Cache Tags <sup>(1)</sup>            |        | Cac    | ne Data |        |

|           |                                      |        |        |         |        |

|           | 금오뛰                                  |        |        |         |        |

|           | LOCK                                 |        |        |         |        |

| 0x1fc01   |                                      | WORD 3 | WORD 2 | WORD 1  | WORD 0 |

|           | → 0x00001300 1 0 1 ···· →            | WORD 3 | WORD 2 | WORD 1  | WORD 0 |

|           | → 0x00001300 1 0 1 ····· →           | WORD 3 | WORD 2 | WORD 1  | WORD 0 |

|           | → 0x00002200 1 0 1                   | WORD 3 | WORD 2 | WORD 1  | WORD 0 |

|           | → 0x80001230 1 0 1                   | WORD 3 | WORD 2 | WORD 1  | WORD 0 |

|           | → 0x00002210 1 0 1 ···· →            | WORD 3 | WORD 2 | WORD 1  | WORD 0 |

|           | → 0x00002230 1 0 1                   | WORD 3 | WORD 2 | WORD 1  | WORD 0 |

|           | → 0x00002220 1 0 1                   | WORD 3 | WORD 2 | WORD 1  | WORD 0 |

|           | → 0x00001200 1 0 1 ····· →           | WORD 3 | WORD 2 | WORD 1  | WORD 0 |

|           | → 0x00001230 0 0 1 ····· →           | WORD 3 | WORD 2 | WORD 1  | WORD 0 |

| нп        |                                      | WORD 3 | WORD 2 | WORD 1  | WORD 0 |

|           | → 0x00001320 1 0 1 ····· →           | WORD 3 | WORD 2 | WORD 1  | WORD 0 |

|           | ► 0x00001330 1 0 0 ►                 | WORD 3 | WORD 2 | WORD 1  | WORD 0 |

|           | → 0x00001310 1 0 0 ····· →           | WORD 3 | WORD 2 | WORD 1  | WORD 0 |

|           | ► 0x00001340 1 0 0 ►                 | WORD 3 | WORD 2 | WORD 1  | WORD 0 |

|           | → 0x00001350 1 0 0 ···· →            | WORD 3 | WORD 2 | WORD 1  | WORD 0 |

Figure 4-2: Cache Look-up Example<sup>(2)</sup>

**Note 1:** Bits 0-3 of the address in the Cache Tags register are always implied '0'.

2: Mask Fields are not shown and are assumed to be '0'.

# 4.2.1 Cache Organization

The cache consists of two arrays: tag and data. A data array could consist of program instructions or program data. The cache is physically tagged and address matches are based on the physical address not the virtual address.

Each line in the tag array contains the following information:

- Mask address mask value

- Tag tag address to match against

- Valid bit

- Lock bit

- Type an instruction and/or data type-indicator bit

Each line in the data array contains 16-bytes of program instruction, or program data, depending on the value of the type-indicator bit.

Figure 4-3 shows the organization of a line. Note that the LMASK (CHEMSK<15:5>) and LTYPE (CHETAG<1>) fields are not programmable for every line. The LTAG (CHETAG<23:4>) field only implements the number of bits needed to fully map to the size of the PFM, e.g., if the Flash size is 512 KB, the LTAG (CHETAG<23:4>) field only implements bits 18 through 4.

| Figure 4-3: | Mask Line |             |      |   |

|-------------|-----------|-------------|------|---|

| 31          | 16        | 15 5        | 4    | 0 |

|             | RSVD      | LMASK<15:5> | RSVD |   |

| Figure 4-4: | Tag Line |            |        |       |      |

|-------------|----------|------------|--------|-------|------|

| 31          | 24       | 23 4       | 32     | 2 1   | 0    |

| LTAGBOOT    | RSVD     | LTAG<23:4> | LVALID | LTYPE | RSVD |

#### Figure 4-5: Data Line

| 31 |        | 0 |

|----|--------|---|

|    | WORD 3 |   |

|    |        |   |

| 31 |        | 0 |

|    | WORD 2 |   |

|    |        |   |

| 31 |        | 0 |

|    | WORD 1 |   |

| 31 |        | 0 |

|    | WORD 0 |   |

|    |        |   |

Cache

Cache arrays are shown in Table 4-1. Software can modify values in both the Tag Line and the Data Line of the cache. Configuration register field CHEIDX (CHEACC<3:0>) selects a line for access. That line can then be modified via the CHETAG, CHEMSK, CHEW0, CHEW1, CHEW2, and CHEW3 registers.

| Table 4-1: | Cache Arrays        |     |   |   |                  |  |  |  |

|------------|---------------------|-----|---|---|------------------|--|--|--|

| Line #     | Tag Array           |     |   |   |                  |  |  |  |

| 0          | 000h <sup>(1)</sup> | TAG | V | L | T(3)             |  |  |  |

| 1          | 000h <sup>(1)</sup> | TAG | V | L | T <sup>(3)</sup> |  |  |  |

| 2          | 000h <sup>(1)</sup> | TAG | V | L | T <sup>(3)</sup> |  |  |  |

| 3          | 000h <sup>(1)</sup> | TAG | V | L | T <sup>(3)</sup> |  |  |  |

| 4          | 000h <sup>(1)</sup> | TAG | V | L | T <sup>(3)</sup> |  |  |  |

| 5          | 000h <sup>(1)</sup> | TAG | V | L | T <sup>(3)</sup> |  |  |  |

| 6          | 000h <sup>(1)</sup> | TAG | V | L | T <sup>(3)</sup> |  |  |  |

| 7          | 000h <sup>(1)</sup> | TAG | V | L | T <sup>(3)</sup> |  |  |  |

| 8          | 000h <sup>(1)</sup> | TAG | V | L | T <sup>(3)</sup> |  |  |  |

| 9          | 000h <sup>(1)</sup> | TAG | V | L | T <sup>(3)</sup> |  |  |  |

| А          | MASK                | TAG | V | L | T <sup>(3)</sup> |  |  |  |

| В          | MASK                | TAG | V | L | T <sup>(3)</sup> |  |  |  |

| С          | 000h <sup>(1)</sup> | TAG | V | L | Т                |  |  |  |

| D          | 000h <sup>(1)</sup> | TAG | V | L | Т                |  |  |  |

| E          | 000h <sup>(1)</sup> | TAG | V | L | Т                |  |  |  |

| F          | 000h <sup>(1)</sup> | TAG | V | L | Т                |  |  |  |

|        | Data Array <sup>(2)</sup> |        |        |  |  |  |  |  |

|--------|---------------------------|--------|--------|--|--|--|--|--|

| Word 3 | Word 2                    | Word 1 | Word 0 |  |  |  |  |  |

| Word 3 | Word 2                    | Word 1 | Word 0 |  |  |  |  |  |

| Word 3 | Word 2                    | Word 1 | Word 0 |  |  |  |  |  |

| Word 3 | Word 2                    | Word 1 | Word 0 |  |  |  |  |  |

| Word 3 | Word 2                    | Word 1 | Word 0 |  |  |  |  |  |

| Word 3 | Word 2                    | Word 1 | Word 0 |  |  |  |  |  |

| Word 3 | Word 2                    | Word 1 | Word 0 |  |  |  |  |  |

| Word 3 | Word 2                    | Word 1 | Word 0 |  |  |  |  |  |

| Word 3 | Word 2                    | Word 1 | Word 0 |  |  |  |  |  |

| Word 3 | Word 2                    | Word 1 | Word 0 |  |  |  |  |  |

| Word 3 | Word 2                    | Word 1 | Word 0 |  |  |  |  |  |

| Word 3 | Word 2                    | Word 1 | Word 0 |  |  |  |  |  |

| Word 3 | Word 2                    | Word 1 | Word 0 |  |  |  |  |  |

| Word 3 | Word 2                    | Word 1 | Word 0 |  |  |  |  |  |

| Word 3 | Word 2                    | Word 1 | Word 0 |  |  |  |  |  |

| Word 3 | Word 2                    | Word 1 | Word 0 |  |  |  |  |  |

Note 1: Read-only field.

2: Read zeros when device is code-protected. Read/write otherwise.

3: Type is fixed as instruction.

It is recommended that cache lines be modified while executing from non-cacheable addresses, since the cache controller does not protect against modifying the cache while executing from cacheable address.

Not all fields are writable. The LMASK (CHEMSK<15:5>) field is only writable for lines 10 and 11, and the LTYPE (CHETAG<1>) field is fixed to the "Instruction" setting for lines 0 through 11.

Note that lines allocated for Lock and Data affect the selection of the line to replace on a miss. However, they do not affect the usage order or pseudo LRU value.

# 4.3 CONTROL REGISTERS

**Note:** Some devices in the PIC32MX family do not contain a prefetch cache module. For these devices, all prefetch cache register locations are reserved and should not be accessed.

The prefetch cache module contains the following Special Functions Registers (SFRs):

CHECON: Prefetch Cache Control Register

Manages configuration of the Prefetch Cache and controls Wait states.

- CHECONCLR, CHECONSET, CHECONINV: Atomic Bit Manipulation Write-only Registers for CHECON

- CHEACC: Prefetch Cache Access Register Points to one of the 16 cache lines to access using the CHETAG, CHEMSK, CHEW0, CHEW1, CHEW2, and CHEW3 registers.

- CHEACCCLR, CHEACCSET, CHEACCINV: Atomic Bit Manipulation Write-only Registers for CHEACC

- CHETAG: Prefetch Cache TAG Register Contains the address and type of information stored in a cache line.

- CHETAGCLR, CHETAGSET, CHETAGINV: Atomic Bit Manipulation Write-only Registers for CHETAG

- CHEMSK: Prefetch Cache TAG Mask Register Provides a mechanism to ignore TAG bits in CHETAG.

- CHEMSKCLR, CHEMSKSET, CHEMSKINV: Atomic Bit Manipulation Write-only Registers for CHEMSK

- CHEW0: Cache Word 0 Register

Provides Access to the Prefetch Cache Data Array

- CHEW1: Cache Word 1 Register

Provides Access to the Prefetch Cache Data Array

- CHEW2: Cache Word 2 Register

Provides Access to the Prefetch Cache Data Array

- CHEW3: Cache Word 3 Register

Provides Access to the Prefetch Cache Data Array

- CHELRU: Cache LRU Register

- CHEHIT: Cache Hit Statistics Register

- CHEMIS: Cache Miss Statistics Register

- PFABT: Prefetch Cache Abort Statistics Register

A statistical register that contains the number of aborted Prefetch Cache operations.

The following table provides a brief summary of prefetch cache-related registers. Corresponding registers appear after the summary, followed by a detailed description of each register.

| Table 4-2: |       |                           | SFRs Sum<br>Bit                                                                                                           | Bit               | Bit               | Di+               | Bit               | Di+              | Dit.             |  |

|------------|-------|---------------------------|---------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Name       |       | Bit<br>31/23/15/7         | Bit<br>30/22/14/6                                                                                                         | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| CHECON     | 31:24 | _                         | —                                                                                                                         | —                 | _                 | —                 | —                 | —                | _                |  |

|            | 23:16 | _                         | _                                                                                                                         | _                 | _                 | _                 | _                 | _                | CHECOH           |  |

|            | 15:8  | _                         | _                                                                                                                         | _                 | _                 | _                 | _                 | DCSZ             | Z<1:0>           |  |

|            | 7:0   | _                         | _                                                                                                                         | PREFE             | N<1:0>            | _                 |                   | PFMWS<2:0:       | >                |  |

| CHECONCLR  | 31:0  |                           | Cle                                                                                                                       | ears selected     | bits in CHECC     | DN, read yield    | s undefined va    | alue             |                  |  |

| CHECONSET  | 31:0  |                           | S                                                                                                                         | ets selected b    | its in CHECO      | N, read yields    | undefined va      | ue               |                  |  |

| CHECONINV  | 31:0  |                           | Sets selected bits in CHECON, read yields undefined value<br>Inverts selected bits in CHECON, read yields undefined value |                   |                   |                   |                   |                  |                  |  |

| CHEACC     | 31:24 | CHEWEN                    | —                                                                                                                         | —                 | —                 | —                 | —                 | —                | —                |  |

|            | 23:16 | —                         | _                                                                                                                         | _                 | —                 | _                 | _                 | —                | _                |  |

|            | 15:8  | —                         | _                                                                                                                         | _                 | —                 | _                 | _                 | —                | _                |  |

|            | 7:0   | _                         | _                                                                                                                         | _                 | _                 |                   | CHEID             | )X<3:0>          |                  |  |

| CHEACCCLR  | 31:0  |                           | Cle                                                                                                                       | ears selected     | bits in CHEAC     | C, read yield     | s undefined va    | alue             |                  |  |

| CHEACCSET  | 31:0  |                           | S                                                                                                                         | ets selected b    | oits in CHEAC     | C, read yields    | undefined val     | ue               |                  |  |

| CHEACCINV  | 31:0  |                           | Ir                                                                                                                        | verts selected    | d bits CHEAC      | C, read yields    | undefined val     | ue               |                  |  |

| CHETAG     | 31:24 | LTAGBOOT                  | _                                                                                                                         | _                 | —                 | _                 | —                 | _                | _                |  |

|            | 23:16 |                           |                                                                                                                           |                   | LTAG<             | <23:16>           |                   |                  |                  |  |

|            | 15:8  |                           |                                                                                                                           |                   | LTAG              | <15:8>            |                   |                  |                  |  |

|            | 7:0   |                           | LTAG                                                                                                                      | <7:4>             |                   | LVALID            | LLOCK             | LTYPE            | _                |  |

| CHETAGCLR  | 31:0  |                           | Cl                                                                                                                        | ears selected     | bits in CHETA     | G, read yields    | s undefined va    | lue              |                  |  |

| CHETAGSET  | 31:0  |                           | S                                                                                                                         | ets selected b    | oits in CHETA     | G, read yields    | undefined val     | ue               |                  |  |

| CHETAGINV  | 31:0  |                           | Ir                                                                                                                        | nverts selecte    | d bits CHETA      | G, read yields    | undefined val     | ue               |                  |  |

| CHEMSK     | 31:24 | _                         | —                                                                                                                         | _                 | —                 | —                 | —                 | _                | _                |  |

|            | 23:16 | _                         |                                                                                                                           |                   | _                 |                   |                   |                  |                  |  |

|            | 15:8  |                           |                                                                                                                           |                   | LMASI             | <15:8>            |                   |                  |                  |  |

|            | 7:0   |                           | LMASK<7:5>                                                                                                                |                   | _                 | _                 | _                 | _                | _                |  |

| CHEMSKCLR  | 31:0  |                           | Cle                                                                                                                       | ears selected     | bits in CHEMS     | SK. read vield:   | s undefined va    | alue             |                  |  |

| CHEMSKSET  | 31:0  |                           |                                                                                                                           |                   | bits in CHEMS     |                   |                   |                  |                  |  |

| CHEMSKINV  | 31:0  |                           |                                                                                                                           |                   | d bits CHEMS      |                   |                   |                  |                  |  |

| CHEW0      | 31:24 |                           |                                                                                                                           |                   |                   | )<31:24>          |                   |                  |                  |  |

|            | 23:16 |                           |                                                                                                                           |                   |                   | )<23:16>          |                   |                  |                  |  |

|            | 15:8  |                           |                                                                                                                           |                   |                   |                   |                   |                  |                  |  |

|            | 7:0   | CHEW0<15:8><br>CHEW0<7:0> |                                                                                                                           |                   |                   |                   |                   |                  |                  |  |

| CHEW1      | 31:24 |                           |                                                                                                                           |                   |                   | <31:24>           |                   |                  |                  |  |

|            | 23:16 |                           |                                                                                                                           |                   | -                 | <23:16>           |                   |                  |                  |  |

|            | 15:8  |                           |                                                                                                                           |                   |                   | 1<15:8>           |                   |                  |                  |  |

|            | 7:0   |                           | CHEW1<7:0>                                                                                                                |                   |                   |                   |                   |                  |                  |  |

| CHEW2      | 31:24 |                           | CHEW2<31:24>                                                                                                              |                   |                   |                   |                   |                  |                  |  |

| -          | 23:16 |                           |                                                                                                                           |                   |                   | 2<23:16>          |                   |                  |                  |  |

|            | 15:8  |                           |                                                                                                                           |                   |                   | 2<15:8>           |                   |                  |                  |  |

|            | 7:0   |                           |                                                                                                                           |                   |                   | /2<7:0>           |                   |                  |                  |  |

| CHEW3      | 31:24 |                           |                                                                                                                           |                   |                   | 3<31:24>          |                   |                  |                  |  |

|            | 23:16 |                           |                                                                                                                           |                   |                   | 3<23:16>          |                   |                  |                  |  |

|            | 15:8  |                           |                                                                                                                           |                   |                   | 3<15:8>           |                   |                  |                  |  |

|            | 10.0  |                           |                                                                                                                           |                   |                   |                   |                   |                  |                  |  |

# Table 4-2: Prefetch Cache SFRs Summary

| Name   |       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| CHELRU | 31:24 |                   |                   |                   |                   |                   |                   |                  | CHELRU<24>       |

|        | 23:16 |                   |                   |                   | CHELRI            | J<23:16>          |                   |                  | I                |

|        | 15:8  |                   |                   |                   | CHELR             | U<15:8>           |                   |                  |                  |

|        | 7:0   |                   |                   |                   | CHELR             | U<7:0>>           |                   |                  |                  |

| CHEHIT | 31:24 |                   |                   |                   | CHEHIT            | <31:24>           |                   |                  |                  |

|        | 23:16 |                   |                   |                   | CHEHIT            | <23:16>           |                   |                  |                  |

|        | 15:8  |                   | CHEHIT<15:8>      |                   |                   |                   |                   |                  |                  |

|        | 7:0   |                   | CHENIT<7:0>       |                   |                   |                   |                   |                  |                  |

| CHEMIS | 31:24 | CHEMIS<31:24>     |                   |                   |                   |                   |                   |                  |                  |

|        | 23:16 | CHEMIS<23:16>     |                   |                   |                   |                   |                   |                  |                  |

|        | 15:8  | CHEMIS<15:8>      |                   |                   |                   |                   |                   |                  |                  |

|        | 7:0   | CHEMIS<7:0>       |                   |                   |                   |                   |                   |                  |                  |

| PFABT  | 31:24 | PFABT<31:24>      |                   |                   |                   |                   |                   |                  |                  |

|        | 23:16 | PFABT<23:16>      |                   |                   |                   |                   |                   |                  |                  |

|        | 15:8  |                   |                   |                   | PFAB              | 「<15:8>           |                   |                  |                  |

|        | 7:0   |                   |                   |                   | PFAB              | T<7:0>            |                   |                  |                  |

Table 4-2:

Prefetch Cache SFRs Summary

Prefetch Cache

|                                                                                                 |                                                                                                                                                                                                                                                                                               | Cache Contro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | - 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                       |                                                                                         |              |        |

|-------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------|--------|

| r-x                                                                                             | r-x                                                                                                                                                                                                                                                                                           | r-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | r-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | r-x                                                                                                                                   | r-x                                                                                     | r-x          | r-x    |

|                                                                                                 | —                                                                                                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | —                                                                                                                                     | —                                                                                       | —            | —      |

| bit 31                                                                                          |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                       |                                                                                         |              | bit 2  |

| r-x                                                                                             | r-x                                                                                                                                                                                                                                                                                           | r-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | r-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | r-x                                                                                                                                   | r-x                                                                                     | r-x          | R/W-0  |

| _                                                                                               | _                                                                                                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                     | —                                                                                       | -            | CHECOH |

| bit 23                                                                                          |                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                       |                                                                                         |              | bit ´  |