# Section 35. Parallel Master Port (PMP)

## HIGHLIGHTS

This section of the manual contains the following major topics:

| 35.1  | Introduction                       |  |

|-------|------------------------------------|--|

| 35.2  | Module Registers                   |  |

| 35.3  | Slave Port Modes                   |  |

| 35.4  | Master Port Modes                  |  |

| 35.5  | Direct Memory Access (DMA) Support |  |

| 35.6  | Application Examples               |  |

| 35.7  | Operation in Power-Saving Modes    |  |

| 35.8  | Register Maps                      |  |

| 35.9  | Related Application Notes          |  |

| 35.10 | ) Revision History                 |  |

35

**Note:** This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device variant, this manual section may not apply to all dsPIC33F/PIC24H devices.

Please consult the note at the beginning of the "**Parallel Master Port (PMP)**" chapter in the current device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com

## 35.1 INTRODUCTION

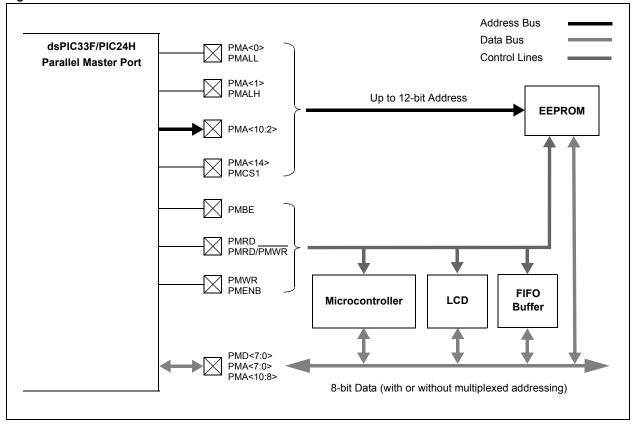

The Parallel Master Port (PMP) is a parallel 8-bit I/O module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. The PMP module is highly configurable because the interface to parallel peripherals varies significantly.

Key features of the PMP module include:

- Eight Data Lines

- Up to 12 Programmable Address Lines

- Single Chip Select Line

- Programmable Strobe Options:

- Individual read and write strobes, or

- Read/Write strobe with enable strobe

- Address Auto-Increment/Auto-Decrement

- Programmable Address/Data Multiplexing

- Programmable Polarity on Control Signals

- Legacy Parallel Slave Port (PSP) Support

- Enhanced Parallel Slave Support:

- Address support

- 4-byte deep auto-incrementing buffer

- Programmable Wait States

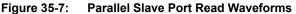

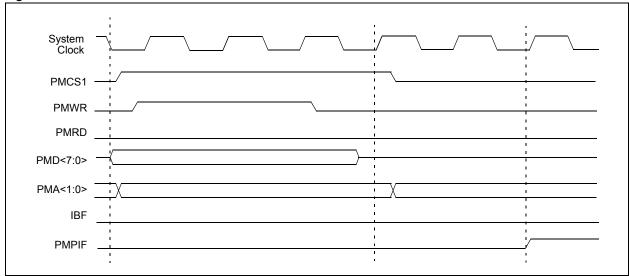

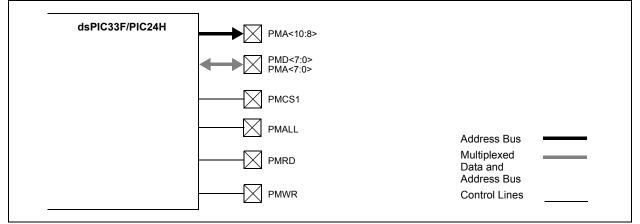

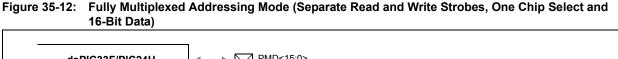

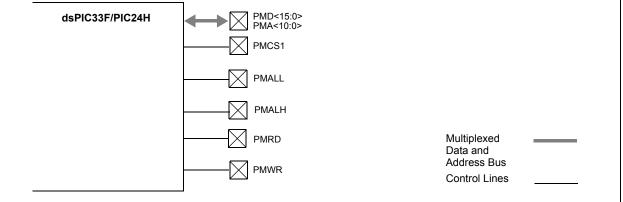

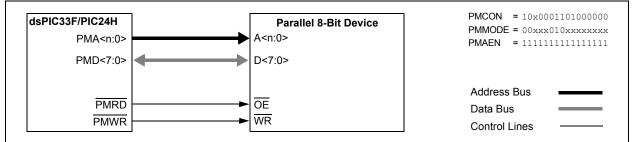

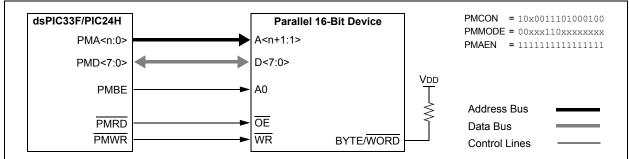

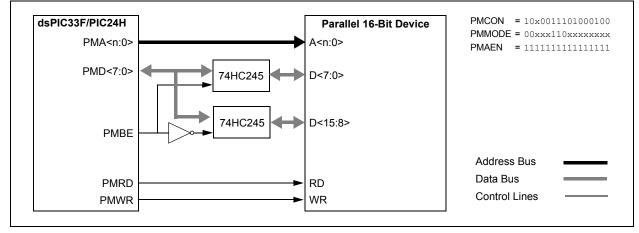

Figure 35-1: PMP Module Pinout and Connections to External Devices

## 35.2 MODULE REGISTERS

The PMP module uses these Special Function Registers (SFRs):

#### • PMCON: Parallel Master Port Control Register

The Parallel Master Port Control register contains the bits that control most of the module's basic functionality. A key bit is PMPEN, which is used to reset the module and enable or disable the module. When the module is disabled, all of the associated I/O pins revert to their designated I/O function. In addition, any read or write operations, active or pending, are stopped and the BUSY bit is cleared. The data within the module registers is retained, including PMSTAT. Therefore, the module can be disabled after a reception, and the last received data and status will be available for processing. When the module is enabled, all buffer control logic is reset along with PMSTAT.

All other bits in the PMCON register control address multiplexing, enable various port control signals, and select control signal polarity. For more information on PMCON bits see **35.4.1** "Parallel Master Port Configuration Options".

#### PMMODE: Parallel Master Port Mode Register

The Parallel Master Port Mode register contains bits that control the operational modes of the module. The Master/Slave mode selection, and configuration options for both the modes, are set by this register. It also contains the universal status flag, BUSY, used in Master modes to indicate that an operation by the module is in progress.

For more information on the use of the PMMODE bits to configure PMP operation, see **35.3 "Slave Port Modes"** and **35.4 "Master Port Modes**".

#### • PMADDR: Parallel Master Port Address Register (Master modes only)<sup>(1)</sup>

Depending on the selected mode, this single register can have one of two functions. In Master modes, the register functions as the Parallel Master Port Address register (PMADDR). It contains the address to which outgoing data is to be written to, as well as the Chip Select control bits for addressing parallel slave devices.

In Slave mode, the register functions as PMDOUT1 and acts as a buffer for outgoing data. Its operation is described in **35.3.2 "Buffered Parallel Slave Port Mode"**.

#### PMAEN: Parallel Master Port Address Enable Register

The Parallel Master Port Address Enable register controls the operation of address and Chip Select pins associated with this module. Setting these bits allocates the corresponding microcontroller pins to the PMP module; clearing these bits allocates the pins to port I/O or other peripheral modules associated with the pins.

#### • PMSTAT: Parallel Master Port Status Register (Slave mode only)

The Parallel Master Port Status register contains status bits associated with buffered operating modes when the port is functioning as a Slave port. This includes the overflow, underflow and full flag bits. For more information on flag bits, see **35.3.2** "**Buffered Parallel Slave Port Mode**".

#### • PMDOUT1: Parallel Master Port Data Output 1 Register (Slave mode only)

For more information on PMDOUT1, see PMADDR: Parallel Master Port Address Register (Master modes only)(1).

#### • PMDOUT2: Parallel Master Port Data Output 2 Register (Slave mode only)

The Parallel Master Port Data Output 2 register is only used in Slave mode for buffered output data. It is used in the same way as PMDOUT1.

#### PMDIN1: Parallel Master Port Data Input 1 Register

The Parallel Master Port Data Input 1 and Data Input 2 registers are used to buffer incoming data. PMDIN1 is used by the module in Master and Slave modes.

In Slave mode, this register is used to hold data that is asynchronously clocked in. Its operation is described in **35.3.2** "Buffered Parallel Slave Port Mode".

In Master mode, PMDIN1 is the holding register for both incoming and outgoing data. Its operation in Master mode is described in **35.4.2** "**Read Operation**" and **35.4.3** "Write **Operation**".

#### • PMDIN2: Parallel Master Port Data Input 2 Register (Buffered Slave mode only)

PMDIN2 is only used in Buffered Slave modes for incoming data. In Buffered Slave modes, its operation is similar to that of PMDIN1.

#### PADCFG1: Pad Configuration Control Register

In addition to the PMP-specific registers, the PADCFG1 register also affects the configuration of the PMP module. The PMPTTL bit (PADCFG1<0>) allows the user application to select between TTL and Schmitt Trigger (ST) digital input buffers for greater compatibility with external circuits. Setting the PMPTTL bit, selects the TTL input buffers. The default configuration is ST buffers.

| R/W-0          | U-0                                                                                                                                   | R/W-0                                   | R/W-0                | R/W-0                | R/W-0            | R/W-0            | R/W-0    |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------------|----------------------|------------------|------------------|----------|--|

| PMPEN          | _                                                                                                                                     | PSIDL                                   | -                    | UX<1:0>              | PTBEEN           | PTWREN           | PTRDEN   |  |

| bit 15         |                                                                                                                                       |                                         |                      |                      |                  |                  | bit 8    |  |

|                |                                                                                                                                       | ~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~~ |                      |                      |                  |                  |          |  |

| R/W-0          | R/W-0                                                                                                                                 | R/W-0 <sup>(1)</sup>                    | U-0                  | R/W-0 <sup>(1)</sup> | R/W-0            | R/W-0            | R/W-0    |  |

| CSF            | -<1:0>                                                                                                                                | ALP                                     | —                    | CS1P                 | BEP              | WRSP             | RDSP     |  |

| bit 7          |                                                                                                                                       |                                         |                      |                      |                  |                  | bit (    |  |

| Legend:        |                                                                                                                                       |                                         |                      |                      |                  |                  |          |  |

| R = Readabl    | e bit                                                                                                                                 | W = Writable                            | bit                  | U = Unimplen         | nented bit, read | d as '0'         |          |  |

| -n = Value at  | Reset                                                                                                                                 | '1' = Bit is set                        |                      | '0' = Bit is clea    |                  | x = Bit is unkn  | iown     |  |

|                |                                                                                                                                       |                                         |                      |                      |                  |                  |          |  |

| bit 15         | PMPEN: Par                                                                                                                            | allel Master Po                         | t Enable bit         |                      |                  |                  |          |  |

|                | 1 = PMP ena                                                                                                                           | bled                                    |                      |                      |                  |                  |          |  |

|                | 0 = PMP disa                                                                                                                          | abled, no off-chi                       | p access perfo       | ormed                |                  |                  |          |  |

| bit 14         | Unimplemer                                                                                                                            | nted: Read as '                         | כי                   |                      |                  |                  |          |  |

| bit 13         | PSIDL: Stop                                                                                                                           | in Idle Mode bit                        | :                    |                      |                  |                  |          |  |

|                | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul> |                                         |                      |                      |                  |                  |          |  |

| bit 12-11      | ADRMUX<1:                                                                                                                             | :0>: Address/Da                         | ata Multiplexin      | g Selection bits     |                  |                  |          |  |

| 11 = Reserved  |                                                                                                                                       |                                         | -                    |                      |                  |                  |          |  |

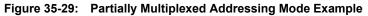

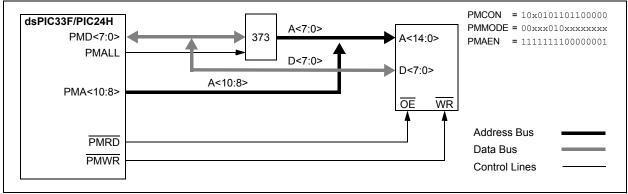

|                |                                                                                                                                       |                                         |                      | on PMD<7:0>          |                  |                  |          |  |

|                |                                                                                                                                       |                                         |                      | ed on PMD<7:0        | > pins, upper 8  | 3 bits are on PN | 1A<10:8> |  |

| bit 10         | 00 = Address and data appear on separate pins<br>PTBEEN: Byte Enable Port Enable bit (16-Bit Master mode)                             |                                         |                      |                      |                  |                  |          |  |

|                | 1 = PMBE port enabled                                                                                                                 |                                         |                      |                      |                  |                  |          |  |

|                | 1 = PMBE pc<br>0 = PMBE pc                                                                                                            |                                         |                      |                      |                  |                  |          |  |

| bit 9          | <b>PTWREN:</b> Write Enable Strobe Port Enable bit                                                                                    |                                         |                      |                      |                  |                  |          |  |

|                | 1 = PMWR/PMENB port enabled                                                                                                           |                                         |                      |                      |                  |                  |          |  |

|                | 0 = PMWR/PMENB port disabled                                                                                                          |                                         |                      |                      |                  |                  |          |  |

| bit 8          | PTRDEN: Re                                                                                                                            | ead/Write Strob                         | e Port Enable        | bit                  |                  |                  |          |  |

|                |                                                                                                                                       | MWR port enab                           |                      |                      |                  |                  |          |  |

|                |                                                                                                                                       | MWR port disat                          |                      |                      |                  |                  |          |  |

| bit 7-6        | CSF<1:0>: Chip Select Function bits                                                                                                   |                                         |                      |                      |                  |                  |          |  |

|                | 11 = Reserved                                                                                                                         |                                         |                      |                      |                  |                  |          |  |

|                | 10 = PMCS1 functions as Chip Select<br>0x = PMCS1 functions as address bit 14                                                         |                                         |                      |                      |                  |                  |          |  |

| bit 5          | ALP: Address Latch Polarity bit <sup>(1)</sup>                                                                                        |                                         |                      |                      |                  |                  |          |  |

|                | 1 = Active-high (PMALL and PMALH)                                                                                                     |                                         |                      |                      |                  |                  |          |  |

|                |                                                                                                                                       | w (PMALL and                            |                      |                      |                  |                  |          |  |

|                | Unimplemer                                                                                                                            | nted: Read as '                         | כ'                   |                      |                  |                  |          |  |

| bit 4          | CS1P: Chip Select 1 Polarity bit <sup>(1)</sup>                                                                                       |                                         |                      |                      |                  |                  |          |  |

| bit 4<br>bit 3 | CS1P: Chip S                                                                                                                          | Select 1 Polarity                       | / bit <sup>(1)</sup> |                      |                  |                  |          |  |

|                | <b>CS1P:</b> Chip :<br>1 = Active-hig<br>0 = Active-low                                                                               | gh                                      | / bit <sup>(1)</sup> |                      |                  |                  |          |  |

| bit 3          | 1 = Active-hi<br>0 = Active-lov                                                                                                       | gh<br>w                                 |                      |                      |                  |                  |          |  |

|                | 1 = Active-hig<br>0 = Active-lov<br><b>BEP:</b> Byte El                                                                               | gh                                      | it                   |                      |                  |                  |          |  |

## Register 35-1: PMCON: Parallel Master Port Control Register

Note 1: These bits have no effect when their corresponding pins are used as address lines.

## Register 35-1: PMCON: Parallel Master Port Control Register (Continued)

| bit 1 | WRSP: Write Strobe Polarity bit                                                                                         |

|-------|-------------------------------------------------------------------------------------------------------------------------|

|       | For Slave Modes and Master Mode 2 (PMMODE<9:8> = 00, 01, 10):                                                           |

|       | 1 = Read strobe active-high (PMWR)<br>0 = Read strobe active-low (PMWR)<br>For Master Mode 1 (PMMODE<9:8> = 11):        |

|       | <ul><li>1 = Enable strobe active-high (PMENB)</li><li>0 = Enable strobe active-low (PMENB)</li></ul>                    |

| bit 0 | RDSP: Read Strobe Polarity bit                                                                                          |

|       | For Slave Modes and Master Mode 2 (PMMODE<9:8> = 00, 01, 10):                                                           |

|       | 1 = Read strobe active-high (PMRD)                                                                                      |

|       | 0 = Read strobe active-low (PMRD)                                                                                       |

|       | For Master Mode 1 (PMMODE<9:8> = 11):                                                                                   |

|       | <ul> <li>1 = Read/write strobe active-high (PMRD/PMWR)</li> <li>0 = Read/write strobe active-low (PMRD/PMWR)</li> </ul> |

Note 1: These bits have no effect when their corresponding pins are used as address lines.

| R-0           | R/W-0                                                                                                                                                                          | R/W-0             | R/W-0           | R/W-0               | R/W-0                                                          | R/W-0           | R/W-0                |  |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----------------|---------------------|----------------------------------------------------------------|-----------------|----------------------|--|

| BUSY          | IRQI                                                                                                                                                                           | M<1:0>            | INC             | M<1:0>              | MODE16                                                         | MODE            | =<1:0>               |  |

| bit 15        |                                                                                                                                                                                |                   |                 |                     |                                                                |                 | bit                  |  |

| R/W-0         | R/W-0                                                                                                                                                                          | R/W-0             | R/W-0           | R/W-0               | R/W-0                                                          | R/W-0           | R/W-0                |  |

| WAITE         | 3<1:0> <sup>(1)</sup>                                                                                                                                                          |                   | WAIT            | <sup>-</sup> M<3:0> |                                                                | WAITE           | <1:0> <sup>(1)</sup> |  |

| bit 7         |                                                                                                                                                                                |                   |                 |                     |                                                                |                 | bit                  |  |

| Legend:       |                                                                                                                                                                                |                   |                 |                     |                                                                |                 |                      |  |

| R = Readabl   | e bit                                                                                                                                                                          | W = Writable      | bit             | U = Unimple         | mented bit, read                                               | as '0'          |                      |  |

| -n = Value at | Reset                                                                                                                                                                          | '1' = Bit is set  |                 | '0' = Bit is cle    | eared                                                          | x = Bit is unkr | iown                 |  |

| bit 15        | BUSY BUSV                                                                                                                                                                      | bit (Master mo    | de only)        |                     |                                                                |                 |                      |  |

|               | 1 = Port is bi                                                                                                                                                                 | -                 | ue only)        |                     |                                                                |                 |                      |  |

|               | 0 = Port is no                                                                                                                                                                 | •                 |                 |                     |                                                                |                 |                      |  |

| bit 14-13     | IRQM<1:0>:                                                                                                                                                                     | Interrupt Requ    | est Mode bits   |                     |                                                                |                 |                      |  |

|               |                                                                                                                                                                                | •                 |                 |                     | Vrite Buffer 3 is w<br>1 (Addressable l                        | •               |                      |  |

|               | 10 = Reserv                                                                                                                                                                    |                   |                 | FWA > 1.0 - 1       |                                                                |                 | y)                   |  |

|               |                                                                                                                                                                                | ot generated at   |                 | read/write cycle    | е                                                              |                 |                      |  |

|               | 00 = No Interrupt generated                                                                                                                                                    |                   |                 |                     |                                                                |                 |                      |  |

| bit 12-11     | INCM<1:0>: Increment Mode bits                                                                                                                                                 |                   |                 |                     |                                                                |                 |                      |  |

|               | <ul> <li>11 = PSP read and write buffers auto-increment (Legacy PSP mode only)</li> <li>10 = Decrement ADDR&lt;15,13:0&gt; by 1 every read/write cycle</li> </ul>              |                   |                 |                     |                                                                |                 |                      |  |

|               |                                                                                                                                                                                | ent ADDR<15,1     |                 |                     |                                                                |                 |                      |  |

|               | 00 = No increment or decrement of address                                                                                                                                      |                   |                 |                     |                                                                |                 |                      |  |

| bit 10        | MODE16: 8-                                                                                                                                                                     | Bit/16-Bit Mode   | bit             |                     |                                                                |                 |                      |  |

|               |                                                                                                                                                                                |                   |                 |                     | to the data registent of the data registence the data register |                 |                      |  |

| bit 9-8       | MODE<1:0>                                                                                                                                                                      | : Parallel Port N | /lode Select bi | ts                  |                                                                |                 |                      |  |

|               | 11 = Master Mode 1 (PMCSx, PMRD/PMWR, PMENB, PMBE, PMA <x:0> and PMD&lt;7:0&gt;)</x:0>                                                                                         |                   |                 |                     |                                                                |                 |                      |  |

|               | 10 = Master Mode 2 (PMCSx, PMRD, PMWR, PMBE, PMA <x:0> and PMD&lt;7:0&gt;)<br/>01 = Enhanced PSP, control signals (PMRD, PMWR, PMCSx, PMD&lt;7:0&gt; and PMA&lt;1:0&gt;)</x:0> |                   |                 |                     |                                                                |                 |                      |  |

|               |                                                                                                                                                                                |                   |                 |                     |                                                                |                 |                      |  |

| bit 7-6       | 00 = Legacy Parallel Slave Port, control signals (PMRD, PMWR, PMCSx and PMD<7:0>) WAITB<1:0>: Data Setup to Read/Write Wait State Configuration bits <sup>(1)</sup>            |                   |                 |                     |                                                                |                 | /                    |  |

|               | 11 = Data wait of 4 Tcy; multiplexed address phase of 4 Tcy                                                                                                                    |                   |                 |                     |                                                                |                 |                      |  |

|               | 10 = Data wait of 3 Tcy; multiplexed address phase of 3 Tcy                                                                                                                    |                   |                 |                     |                                                                |                 |                      |  |

|               |                                                                                                                                                                                | ait of 2 TCY; mu  |                 |                     |                                                                |                 |                      |  |

| bit 5-2       |                                                                                                                                                                                | ait of 1 TCY; mu  | -               | -                   |                                                                |                 |                      |  |

| DIL 3-2       | WAITM<3:0>: Read to Byte Enable Strobe Wait State Configuration bits                                                                                                           |                   |                 |                     |                                                                |                 |                      |  |

|               | 1111 = Wait of additional 15 Tcy                                                                                                                                               |                   |                 |                     |                                                                |                 |                      |  |

|               | •                                                                                                                                                                              |                   |                 |                     |                                                                |                 |                      |  |

|               | •                                                                                                                                                                              |                   |                 |                     |                                                                |                 |                      |  |

|               |                                                                                                                                                                                | of additional 1   | Tov             |                     |                                                                |                 |                      |  |

| Register 35-2: | PMMODE: Parallel Master Port Mode Register |

|----------------|--------------------------------------------|

|----------------|--------------------------------------------|

## Register 35-2: PMMODE: Parallel Master Port Mode Register (Continued)

- bit 1-0 WAITE<1:0>: Data Hold After Strobe Wait State Configuration bits<sup>(1)</sup>

- 11 = Wait of 4 Tcy 10 = Wait of 3 Tcy 01 = Wait of 2 Tcy

- 00 = Wait of 1 Tcy

- **Note 1:** WAITBx and WAITEx bits are ignored whenever WAITM<3:0> = 0000.

- 2: WAITM<3:0> and WAITE<1:0> bits are ignored when WAITB<1:0> bits determine the duration of the address latch signal.

| U-0<br>                                                                        | U-0<br>–<br>R/W-0<br>ADDF                               | U-0<br>—<br>R/W-0<br>R<7:0><br>U = Unimple<br>'0' = Bit is cl |                                      |                                                         | R/W-0                                                       |  |  |  |  |  |  |

|--------------------------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------------------------|--------------------------------------|---------------------------------------------------------|-------------------------------------------------------------|--|--|--|--|--|--|

| Writable bit                                                                   |                                                         | R<7:0><br>U = Unimple                                         | emented bit, read                    | R/W-0                                                   |                                                             |  |  |  |  |  |  |

| Writable bit                                                                   |                                                         | R<7:0><br>U = Unimple                                         | emented bit, read                    | d as '0'                                                | R/W-0                                                       |  |  |  |  |  |  |

| Writable bit                                                                   |                                                         | R<7:0><br>U = Unimple                                         | emented bit, read                    | d as '0'                                                |                                                             |  |  |  |  |  |  |

| Writable bit                                                                   |                                                         | R<7:0><br>U = Unimple                                         | emented bit, read                    | d as '0'                                                |                                                             |  |  |  |  |  |  |

|                                                                                | ADDF                                                    | U = Unimple                                                   |                                      |                                                         | bit 0                                                       |  |  |  |  |  |  |

|                                                                                |                                                         | •                                                             |                                      |                                                         | bit 0                                                       |  |  |  |  |  |  |

|                                                                                |                                                         | •                                                             |                                      |                                                         |                                                             |  |  |  |  |  |  |

|                                                                                |                                                         | •                                                             |                                      |                                                         |                                                             |  |  |  |  |  |  |

|                                                                                |                                                         | •                                                             |                                      |                                                         |                                                             |  |  |  |  |  |  |

| Bit is set                                                                     |                                                         | '0' = Bit is cl                                               |                                      |                                                         | e bit U = Unimplemented bit, read as '0'                    |  |  |  |  |  |  |

|                                                                                |                                                         | o Bitiooi                                                     | eared                                | x = Bit is unkr                                         | IOWN                                                        |  |  |  |  |  |  |

| Read as '∩'                                                                    |                                                         |                                                               |                                      |                                                         |                                                             |  |  |  |  |  |  |

| Unimplemented: Read as '0'<br>CS1: Chip Select 1 bit <sup>(2)</sup>            |                                                         |                                                               |                                      |                                                         |                                                             |  |  |  |  |  |  |

| 14 <b>CS1:</b> Chip Select 1 bit <sup>(2)</sup><br>1 = Chip Select 1 is active |                                                         |                                                               |                                      |                                                         |                                                             |  |  |  |  |  |  |

| s inactive                                                                     |                                                         |                                                               |                                      |                                                         |                                                             |  |  |  |  |  |  |

| Unimplemented: Read as '0'                                                     |                                                         |                                                               |                                      |                                                         |                                                             |  |  |  |  |  |  |

| tination Addre                                                                 | ess bits 10                                             | -0                                                            |                                      |                                                         |                                                             |  |  |  |  |  |  |

| 5                                                                              | bit <sup>(2)</sup><br>active<br>inactive<br>Read as '0' | bit( <b>2)</b><br>active<br>inactive<br>Read as '0'           | bit <b>(2)</b><br>active<br>inactive | bit <sup>(2)</sup><br>active<br>inactive<br>Read as '0' | bit <sup>(2)</sup><br>; active<br>; inactive<br>Read as '0' |  |  |  |  |  |  |

## Register 35-3: PMADDR: Parallel Master Port Address Register (Master modes only)<sup>(1)</sup>

- For more information, see **35.2 "Module Registers"**.

- **2:** When CSF<1:0> = 0x, CS1 bit functions as ADDR<14>.

| U-0                                  | R/W-0                                       | U-0               | U-0            | U-0               | R/W-0          | R/W-0           | R/W-0 |  |  |

|--------------------------------------|---------------------------------------------|-------------------|----------------|-------------------|----------------|-----------------|-------|--|--|

| _                                    | — PTEN — —                                  |                   |                |                   |                | PTEN<10:8>      |       |  |  |

| bit 15                               |                                             |                   |                |                   |                |                 | bit   |  |  |

|                                      | <b></b>                                     |                   |                |                   | <b>D</b> 444 A | <b>D</b> 444 A  |       |  |  |

| R/W-0                                | R/W-0                                       | R/W-0             | R/W-0          | R/W-0             | R/W-0          | R/W-0           | R/W-0 |  |  |

|                                      |                                             |                   | PTEN           | N<7:0>            |                |                 |       |  |  |

| bit 7                                |                                             |                   |                |                   |                |                 | bit ( |  |  |

| Logondu                              |                                             |                   |                |                   |                |                 |       |  |  |

| Legend:                              |                                             |                   |                |                   |                |                 |       |  |  |

| R = Readable bit W = Writable bit    |                                             |                   | U = Unimplem   | iented bit, rea   | d as '0'       |                 |       |  |  |

| -n = Value at Reset (1' = Bit is set |                                             |                   |                | '0' = Bit is clea | ared           | x = Bit is unkr | iown  |  |  |

|                                      |                                             |                   |                |                   |                |                 |       |  |  |

| bit 15                               | Unimplemented: Read as '0'                  |                   |                |                   |                |                 |       |  |  |

| bit 14                               | PTEN<14>: PMCS1 Strobe Enable bit           |                   |                |                   |                |                 |       |  |  |

|                                      |                                             | unctions as eithe |                | or PMCS1          |                |                 |       |  |  |

|                                      | 0 = PMA14 functions as port I/O             |                   |                |                   |                |                 |       |  |  |

| bit 13-11                            | Unimplemented: Read as '0'                  |                   |                |                   |                |                 |       |  |  |

| bit 10-2                             | PTEN<10:2>                                  | : PMP Address     | Port Enable b  | its               |                |                 |       |  |  |

|                                      | 1 = PMA<10:2> function as PMP address lines |                   |                |                   |                |                 |       |  |  |

|                                      | 0 = PMA<10:                                 | 2> function as p  | ort I/O        |                   |                |                 |       |  |  |

| bit 1-0                              | PTEN<1:0>:                                  | PMALH/PMALL       | Strobe Enabl   | le bits           |                |                 |       |  |  |

|                                      | 1 = PMA1 an                                 | d PMA0 function   | n as either PN | 1A<1:0> or PMA    | LH and PMA     | _L              |       |  |  |

|                                      | ∩ = PMΔ1 an                                 | d PMA0 function   | n as nort I/O  |                   |                |                 |       |  |  |

#### Register 35-4: PMAEN: Parallel Master Port Address Enable Register

0 = PMA1 and PMA0 function as port I/O

35

# dsPIC33F/PIC24H Family Reference Manual

| R-0           | R/W-0 HS                                                                                                                                                                  | U-0              | U-0   | R-0                   | R-0             | R-0             | R-0   |  |  |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-------|-----------------------|-----------------|-----------------|-------|--|--|

| IBF           | IBOV                                                                                                                                                                      | <u> </u>         | —     | IB3F                  | IB2F            | IB1F            | IB0F  |  |  |

| bit 15        |                                                                                                                                                                           |                  |       |                       |                 |                 | bit 8 |  |  |

|               |                                                                                                                                                                           |                  |       |                       |                 |                 |       |  |  |

| R-1           | R/W-0 HS                                                                                                                                                                  | U-0              | U-0   | R-1                   | R-1             | R-1             | R-1   |  |  |

| OBE           | OBUF                                                                                                                                                                      | —                |       | OB3E                  | OB2E            | OB1E            | OB0E  |  |  |

| bit 7         |                                                                                                                                                                           |                  |       |                       |                 |                 | bit ( |  |  |

| Legend:       |                                                                                                                                                                           | HS = Hardwar     | e Set | HC = Hardware Cleared |                 |                 |       |  |  |

| R = Readabl   | e bit                                                                                                                                                                     | W = Writable I   | oit   | U = Unimplem          | ented bit, read | 1 as '0'        |       |  |  |

| -n = Value at | Reset                                                                                                                                                                     | '1' = Bit is set |       | '0' = Bit is clea     |                 | x = Bit is unkn | own   |  |  |

|               |                                                                                                                                                                           |                  |       |                       |                 |                 |       |  |  |

| bit 15        | IBF: Input Bu                                                                                                                                                             | ffer Full Status | bit   |                       |                 |                 |       |  |  |

|               | 1 = All writable input buffer registers are fu                                                                                                                            |                  |       |                       |                 |                 |       |  |  |

|               | 0 = Some or all the writable input buffer registers are empty                                                                                                             |                  |       |                       |                 |                 |       |  |  |

| bit 14        | <b>IBOV:</b> Input Buffer Overflow Status bit                                                                                                                             |                  |       |                       |                 |                 |       |  |  |

|               | <ul> <li>1 = A write attempt to a full input byte register occurred (must be cleared in software)</li> <li>0 = No overflow occurred</li> </ul>                            |                  |       |                       |                 |                 |       |  |  |

| bit 13-12     | Unimplemented: Read as '0'                                                                                                                                                |                  |       |                       |                 |                 |       |  |  |

| bit 11-8      | IBnF: Input Buffer 'n' Status Full bit                                                                                                                                    |                  |       |                       |                 |                 |       |  |  |

|               | <ul> <li>1 = Input buffer contains data that has not been read (reading buffer will clear this bit)</li> <li>0 = Input buffer does not contain any unread data</li> </ul> |                  |       |                       |                 |                 |       |  |  |

| bit 7         | OBE: Output Buffer Empty Status bit                                                                                                                                       |                  |       |                       |                 |                 |       |  |  |

|               | <ul> <li>1 = All readable output buffer registers are empty</li> <li>0 = Some or all of the readable output buffer registers are full</li> </ul>                          |                  |       |                       |                 |                 |       |  |  |

| bit 6         | <b>OBUF:</b> Output Buffer Underflow Status bit                                                                                                                           |                  |       |                       |                 |                 |       |  |  |

|               | <ul> <li>1 = A read occurred from an empty output byte register (must be cleared in software)</li> <li>0 = No underflow occurred</li> </ul>                               |                  |       |                       |                 |                 |       |  |  |

| bit 5-4       | Unimplemen                                                                                                                                                                | ted: Read as '   | )'    |                       |                 |                 |       |  |  |

|               | <b>OBnE:</b> Output Buffer 'n' Status Empty bit                                                                                                                           |                  |       |                       |                 |                 |       |  |  |

| bit 3-0       | OBIL: Output                                                                                                                                                              |                  |       |                       |                 |                 |       |  |  |

## Register 35-5: PMSTAT: Parallel Master Port Status Register (Slave mode only)

| U-0                               | U-0 | U-0                                                                                            | U-0                                                               | U-0                                                                                                                                                                                     | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |

|-----------------------------------|-----|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                   |     |                                                                                                |                                                                   | _                                                                                                                                                                                       | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |

|                                   |     |                                                                                                |                                                                   |                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | bit 8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

|                                   |     |                                                                                                |                                                                   |                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

| U-0                               | U-0 | U-0                                                                                            | U-0                                                               | U-0                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |

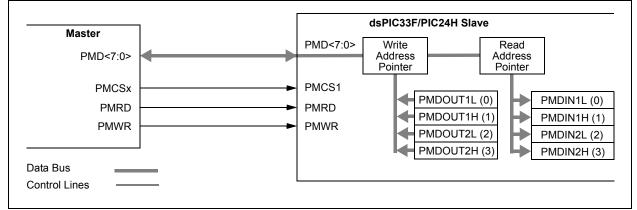

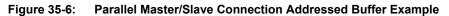

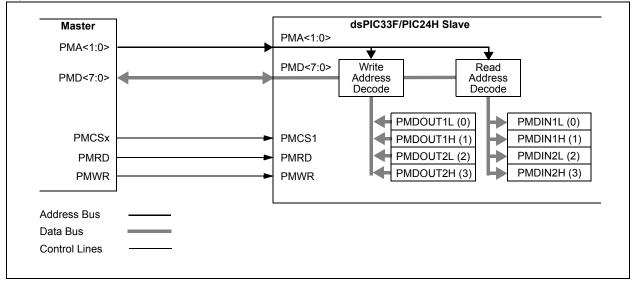

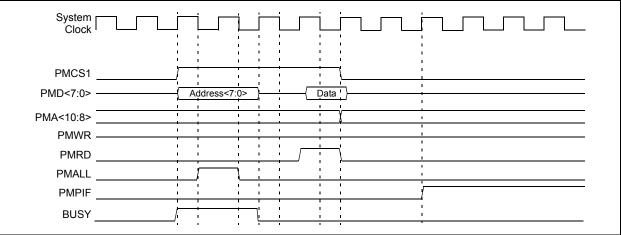

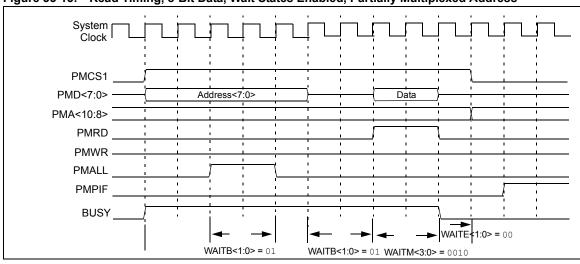

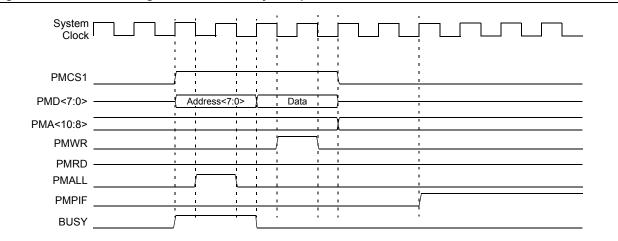

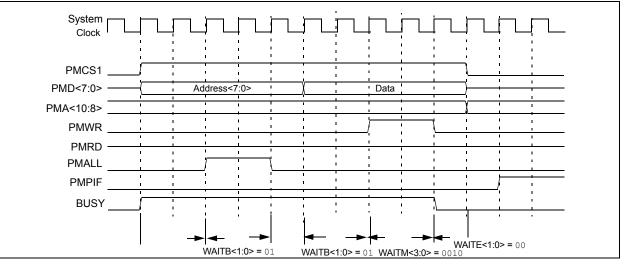

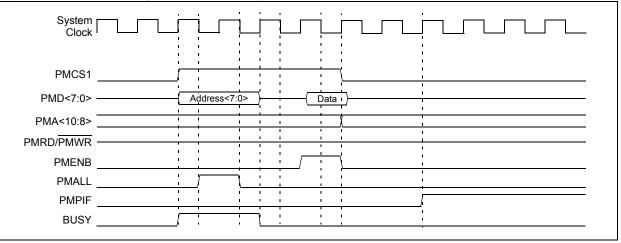

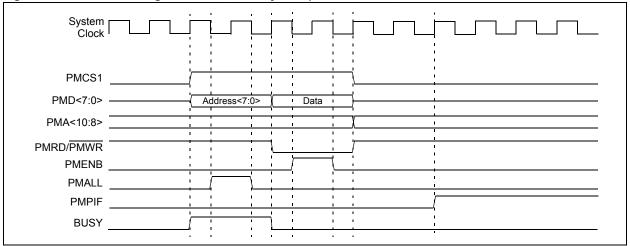

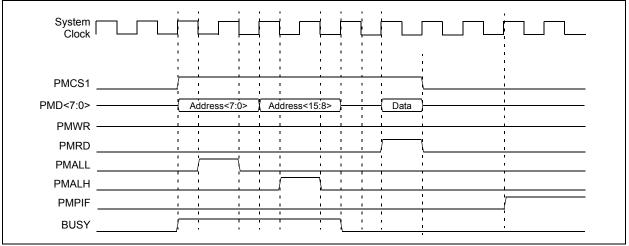

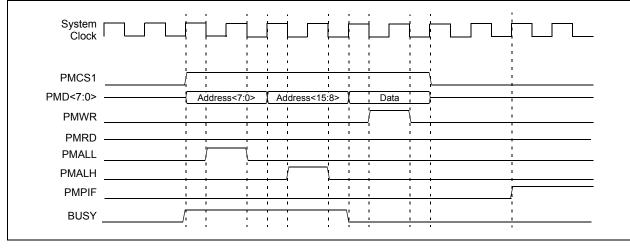

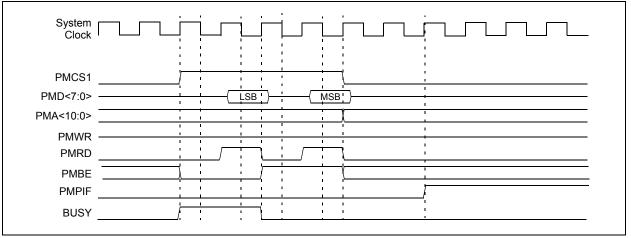

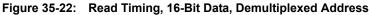

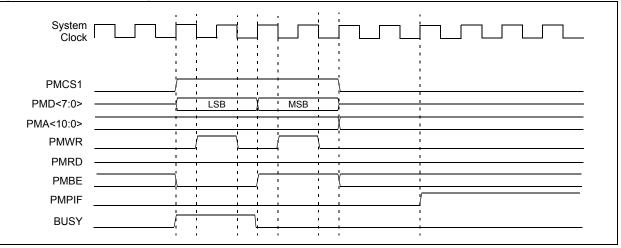

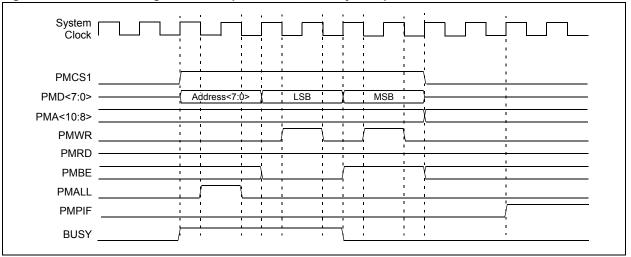

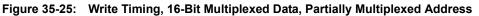

|                                   |     |                                                                                                | —                                                                 | _                                                                                                                                                                                       | RTSECSEL <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PMPTTL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |