# Section 14. Motor Control PWM

# HIGHLIGHTS

This section of the manual contains the following topics:

| 14.1  | Introduction                         | 14-2  |

|-------|--------------------------------------|-------|

| 14.2  | Features of the MCPWM1 Module        | 14-2  |

| 14.3  | Features of the MCPWM2 Module        | 14-3  |

| 14.4  | Register Descriptions                | 14-4  |

| 14.5  | Special Function Registers           | 14-6  |

| 14.6  | MCPWM Module Architecture Overview   | 14-20 |

| 14.7  | MCPWM Module Operating Modes         | 14-22 |

| 14.8  | PWM Clock Control                    | 14-23 |

| 14.9  | Time Base Interrupts                 | 14-26 |

| 14.10 | PWM Output State Control             | 14-27 |

| 14.11 | PWM Output Modes                     | 14-28 |

| 14.12 | Duty Cycle Register Buffering        | 14-32 |

| 14.13 | PWM Duty Cycle Resolution            | 14-34 |

|       | PWM Dead Time Control                |       |

| 14.15 | PWM Fault Handling                   | 14-40 |

| 14.16 | Special Features of the MCPWM Module | 14-43 |

| 14.17 | Operation in Power-Saving Modes      | 14-49 |

| 14.18 | Related Application Notes            | 14-52 |

| 14.19 | Revision History                     | 14-53 |

|       |                                      |       |

Motor Control

**Note:** This family reference manual section is meant to serve as a complement to device data sheets. Depending on the device variant, this manual section may not apply to all dsPIC33F/PIC24H devices.

Please consult the note at the beginning of the "**Motor Control PWM**" chapter in the current device data sheet to check whether this document supports the device you are using.

Device data sheets and family reference manual sections are available for download from the Microchip Worldwide Web site at: http://www.microchip.com

# 14.1 INTRODUCTION

This section describes the Motor Control PWM (MCPWM) peripheral in the dsPIC33F/PIC24H family of devices.

#### 14.1.1 Purpose of the MCPWM Module

The MCPWM is used to generate a periodic pulse waveform, which is useful in motor and power control applications. The MCPWM module acts as a timer to count up to a period count value. The time period and the duty cycle of the pulses are both programmable.

Depending on the device variant, there are up to two MCPWM modules, MCPWM1 and MCPWM2, in the dsPIC33F/PIC24H family of devices. The features of these two modules are listed in sections 14.2 "Features of the MCPWM1 Module" and 14.3 "Features of the MCPWM2 Module".

# 14.2 FEATURES OF THE MCPWM1 MODULE

The MCPWM1 module is used to generate multiple synchronized pulse-width modulated outputs. The following motor and power control applications are supported by the MCPWM1 module:

- Three-Phase AC Induction Motor (ACIM)

- Switched Reluctance Motor

- · Brushless DC (BLDC) Motor

- Uninterruptible Power Supply (UPS)

The distinctive features of the MCPWM1 module are summarized below:

- · Up to eight PWM outputs with four duty cycle generators

- · Dedicated time base that supports TCY/2 PWM edge resolution

- On-the-fly PWM frequency changes

- Hardware dead time generators

- · Output pin polarity programmed by device configuration bits

- Multiple operating and output modes:

- Single event mode

- Edge-aligned mode

- Center-aligned mode

- Center-aligned mode with double updates

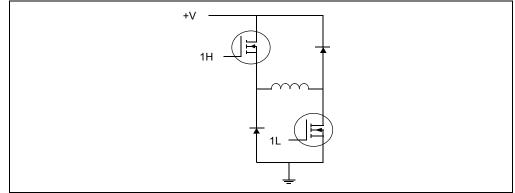

- Complementary output mode

- Independent output mode

- · Manual override register for PWM output pins

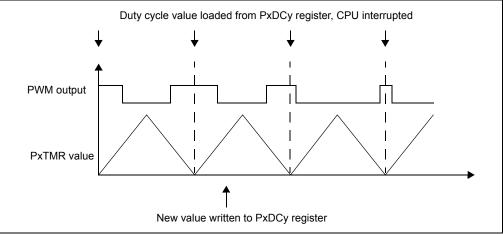

- · Duty cycle updates that can be configured to be immediate or synchronized to the PWM

- · Up to two hardware fault input pins with programmable function

- Special Event Trigger for synchronizing analog-to-digital conversions

- · Output pins associated with the PWM can be individually enabled

**Note:** Depending on the dsPIC33F/PIC24H device variant, there are different versions of the MCPWM1 module. Refer to the specific device data sheet for further details.

# 14.3 FEATURES OF THE MCPWM2 MODULE

The MCPWM2 module provides a pair of complementary PWM outputs, which are useful in the following applications:

- · Independent Power Factor Correction (PFC) in a motor system

- · Induction cooking systems

- DC motor control systems

- Single-phase inverter control

- Single-phase ACIM control

The distinctive features of the MCPWM2 module are summarized below:

- · Two PWM outputs with one duty cycle generator

- Dedicated time base that supports Tcy/2 PWM edge resolution

- On-the-fly PWM frequency changes

- Hardware dead time generator

- · Output pin polarity programmed by device configuration bits

- Multiple output and operating modes:

- Single Event mode

- Edge-Aligned mode

- Center-Aligned mode

- Center-Aligned mode with double updates

- Complementary Operating mode

- · Manual override register for PWM output pins

- · Duty cycle updates that can be configured to be immediate or synchronized to the PWM

- A hardware fault input pin with programmable function

- · Special Event Trigger for synchronizing analog-to-digital conversions

- Output pins associated with the PWM that can be individually enabled

**Note:** The MCPWM2 module is present only in specific dsPIC33F/PIC24H devices. Refer to the specific device data sheet for further details.

Motor Control

© 2010 Microchip Technology Inc.

# 14.4 REGISTER DESCRIPTIONS

The following registers are used to control the operation of the MCPWM1 and MCPWM2 modules:

**Note:** The letter "x" in the register names refers to the MCPWM module number.

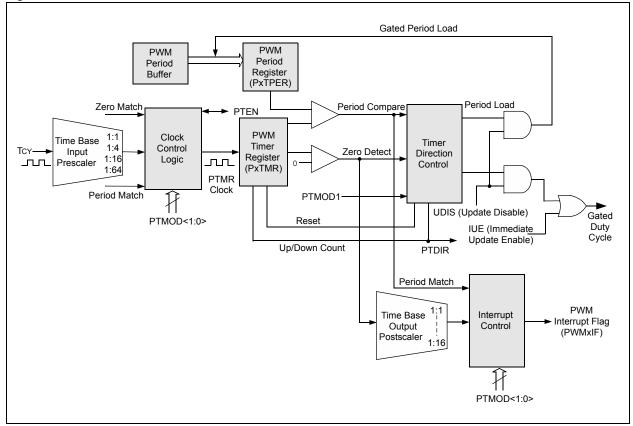

#### • PxTCON: PWM Time Base Control Register

This register is used for the selection of the Time Base mode, time base input clock prescaler, and time base output postscaler, and for enabling the time base timer.

#### • PxTMR: PWM Time Base Register

The time base count value and the time base count direction status are obtained in this register.

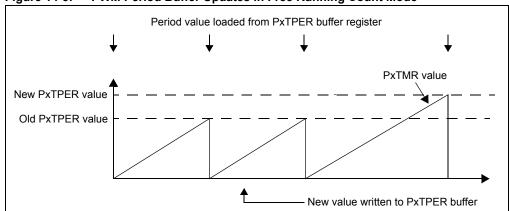

#### PxTPER: PWM Time Base Period Register

The PWM time base value is written into this register, which determines the PWM operating frequency.

#### • PxSECMP: Special Event Compare Register

This register provides the compare value at which the analog-to-digital conversions are to be synchronized with the PWM time base. Comparison can be either during up-count or down-count in Center-aligned mode depending on the setting of the SEVTDIR bit in this register.

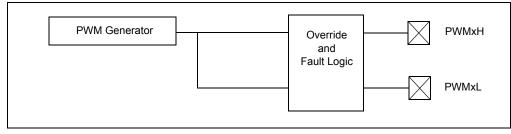

#### PWMxCON1: PWM Control Register 1

Selection of either Independent or Complementary mode for each PWM I/O pair is performed in this register.

#### PWMxCON2: PWM Control Register 2

This register provides the following selections:

- Selection of a PWM Special Event Trigger output postscaler value

- Immediate updating of duty cycle registers

- Selection of output override synchronization with the time base

- Enabling updates from duty cycle and period buffer registers

#### • PxDTCON1: Dead Time Control Register 1

The dead time value and clock period prescaler for Dead Time Unit A and Dead Time Unit B can be selected using this register.

#### • PxDTCON2: Dead Time Control Register 2

Dead time insertions from Dead Time Unit A or Dead Time Unit B for each of the PWM outputs can be selected using this register.

#### • PxFLTACON: Fault A Control Register

This register provides the following selections:

- PWM output pin driven on an external fault active or inactive state

- Fault mode Cycle-by-Cycle mode or Latched mode

- Pin pair to be controlled or not controlled by Fault Input A

#### • PxFLTBCON: Fault B Control Register

The following selections can be done using this register:

- PWM output pin driven on an external fault active or inactive state

- Fault mode Cycle-by-Cycle mode or Latched mode

- Pin pair to be controlled or not controlled by Fault Input B

#### PxOVDCON: Override Control Register

This register is used for enabling the output override feature and for PWM output pin control selection.

• PxDC1: PWM Duty Cycle Register 1

The 16-bit PWM Duty Cycle value for PWM output pair 1 is written into this register.

- PxDC2: PWM Duty Cycle Register 2 The 16-bit PWM Duty Cycle value for PWM output pair 2 is written into this register.

- PxDC3: PWM Duty Cycle Register 3

The 16-bit PWM Duty Cycle value for PWM output pair 3 is written into this register.

• PxDC4: PWM Duty Cycle Register 4

The 16-bit PWM Duty Cycle value for PWM output pair 4 is written into this register.

• PWMKEY: PWM Unlock Register

This register enables the user to unlock the PWMxCON1, PxFLTACON and PxFLTBCON registers for write access.

FPOR: POR Device Configuration Register

In addition to the Special Function Registers (SFRs) associated with the MCPWM module, three device configuration bits can be used to set up the initial Reset states and polarity of the PWM I/O pins. These configuration bits are located in the FPOR register.

#### FOSCSEL: Oscillator Source Selection Register

In addition to the Special Function Registers (SFRs) associated with the MCPWM module, one device Configuration bit in this register can be used to set up the write-protect feature of the PWM Configuration registers.

# 14

Motor Contro PWM

# 14.5 SPECIAL FUNCTION REGISTERS

| R/W-0     | 0-U 0                                                                        | R/W-0                                    | U-0                                | U-0                             | U-0            | U-0             | U-0       |  |  |  |

|-----------|------------------------------------------------------------------------------|------------------------------------------|------------------------------------|---------------------------------|----------------|-----------------|-----------|--|--|--|

| PTEN      | ı —                                                                          | PTSIDL                                   | _                                  |                                 |                |                 | _         |  |  |  |

| bit 15    |                                                                              |                                          |                                    |                                 |                |                 | bit       |  |  |  |

| R/W-0     | 0 R/W-0                                                                      | R/W-0                                    | R/W-0                              | R/W-0                           | R/W-0          | R/W-0           | R/W-0     |  |  |  |

|           | PTOF                                                                         | PS<3:0>                                  |                                    | PTCKP                           | S<1:0>         | PTMO            | D<1:0>    |  |  |  |

| bit 7     |                                                                              |                                          |                                    |                                 |                |                 | bit       |  |  |  |

| Legend:   |                                                                              |                                          |                                    |                                 |                |                 |           |  |  |  |

| R = Read  | dable bit                                                                    | W = Writable bit                         | L                                  | I = Unimplemer                  | nted bit, read | as '0'          |           |  |  |  |

| -n = Valu | e at POR                                                                     | '1' = Bit is set                         | "(                                 | )' = Bit is cleare              | ed             | x = Bit is unkn | own       |  |  |  |

| bit 15    | <b>PTEN:</b> PWM Time                                                        |                                          | le bit                             |                                 |                |                 |           |  |  |  |

|           | 0 = PWM time bas                                                             |                                          |                                    |                                 |                |                 |           |  |  |  |

| bit 14    | Unimplemented: Read as '0'                                                   |                                          |                                    |                                 |                |                 |           |  |  |  |

| bit 13    | PTSIDL: PWM Time Base Stop in Idle Mode bit                                  |                                          |                                    |                                 |                |                 |           |  |  |  |

|           | 1 = PWM time bas<br>0 = PWM time bas                                         | e halts in CPU Idle                      | e mode                             |                                 |                |                 |           |  |  |  |

| bit 12-8  | Unimplemented: Read as '0'                                                   |                                          |                                    |                                 |                |                 |           |  |  |  |

| bit 7-4   | PTOPS<3:0>: PWM Time Base Output Postscale Select bits                       |                                          |                                    |                                 |                |                 |           |  |  |  |

|           | 1111 = 1:16 postscale                                                        |                                          |                                    |                                 |                |                 |           |  |  |  |

|           | •                                                                            |                                          |                                    |                                 |                |                 |           |  |  |  |

|           | •                                                                            |                                          |                                    |                                 |                |                 |           |  |  |  |

|           | •                                                                            |                                          |                                    |                                 |                |                 |           |  |  |  |

|           | 0001 = 1:2 postscale<br>0000 = 1:1 postscale                                 |                                          |                                    |                                 |                |                 |           |  |  |  |

| bit 3-2   | PTCKPS<1:0>: PV                                                              | VM Time Base Inp                         | out Clock Pres                     | cale Select bits                | 3              |                 |           |  |  |  |

|           | 11 = PWM time ba<br>10 = PWM time ba<br>01 = PWM time ba<br>00 = PWM time ba | se input clock per<br>se input clock per | iod is 16 Tcy (<br>iod is 4 Tcy (1 | (1:16 prescale)<br>:4 prescale) |                |                 |           |  |  |  |

| bit 1-0   | PTMOD<1:0>: PW                                                               | M Time Base Mod                          | de Select bits                     |                                 |                |                 |           |  |  |  |

|           | 11 = PWM time ba<br>10 = PWM time ba<br>01 = PWM time ba<br>00 = PWM time ba | se operates in a C<br>se operates in Sir | Continuous Up<br>ngle Event mo     | /Down Countin<br>de             |                | for double PW   | M updates |  |  |  |

#### Register 14-1: PxTCON: PWM Time Base Control Register

| R-0           | R/W-0                              | R/W-0 | R/W-0 | R/W-0                          | R/W-0  | R/W-0          | R/W-0 |  |

|---------------|------------------------------------|-------|-------|--------------------------------|--------|----------------|-------|--|

| PTDIR         |                                    |       |       | PTMR<14:8>                     |        |                |       |  |

| bit 15        |                                    |       |       |                                |        |                | bit 8 |  |

|               |                                    |       |       |                                |        |                |       |  |

| R/W-0         | R/W-0                              | R/W-0 | R/W-0 | R/W-0                          | R/W-0  | R/W-0          | R/W-0 |  |

|               |                                    |       | PTMR< | <7:0>                          |        |                |       |  |

| bit 7         |                                    |       |       |                                |        |                | bit 0 |  |

|               |                                    |       |       |                                |        |                |       |  |

| Legend:       |                                    |       |       |                                |        |                |       |  |

| R = Readable  | R = Readable bit W = Writable bit  |       |       | U = Unimplemented, read as '0' |        |                |       |  |

| -n = Value at | -n = Value at POR '1' = Bit is set |       |       | '0' = Bit is c                 | leared | x = Bit is unł | known |  |

#### Register 14-2: PxTMR: PWM Time Base Register

bit 15 PTDIR: PWM Time Base Count Direction Status bit (read-only)

1 = PWM time base is counting down

0 = PWM time base is counting up

bit 14-0 **PTMR<14:0>:** PWM Time Base Register Count Value bits

#### Register 14-3: PxTPER: PWM Time Base Period Register

| Legend:<br>R = Readable | bit   | W = Writabl | e bit | U = Unimple | emented, read | as '0' |       |  |  |

|-------------------------|-------|-------------|-------|-------------|---------------|--------|-------|--|--|

| bit 7                   |       |             |       |             |               |        | bit 0 |  |  |

|                         |       |             | PTPER | <7:0>       |               |        |       |  |  |

| R/W-0                   | R/W-0 | R/W-0       | R/W-0 | R/W-0       | R/W-0         | R/W-0  | R/W-0 |  |  |

| bit 15                  |       |             |       |             |               |        | bit 8 |  |  |

| —                       | _     |             |       |             | PTPER <14:8>  |        |       |  |  |

| U-0                     | R/W-0 | R/W-0       | R/W-0 | R/W-0       | R/W-0         | R/W-0  | R/W-0 |  |  |

'0' = Bit is cleared

bit 15 Unimplemented: Read as '0'

-n = Value at POR

bit 14-0 PTPER<14:0>: PWM Time Base Period Value bits

'1' = Bit is set

Motor Control PWM

x = Bit is unknown

| R/W-0                             | R/W-0         | R/W-0            | R/W-0                          | R/W-0                | R/W-0 | R/W-0              | R/W-0 |  |  |

|-----------------------------------|---------------|------------------|--------------------------------|----------------------|-------|--------------------|-------|--|--|

| SEVTDIR                           | SEVTCMP<14:8> |                  |                                |                      |       |                    |       |  |  |

| bit 15                            |               |                  |                                |                      |       |                    | bit 8 |  |  |

| DAMA                              | DAMA          | DAMA             | <b>D</b> 444 0                 | DAMA                 | DAMA  | <b>D</b> 444 0     | DAVA  |  |  |

| R/W-0                             | R/W-0         | R/W-0            | R/W-0                          | R/W-0                | R/W-0 | R/W-0              | R/W-0 |  |  |

|                                   |               |                  | SEVTCM                         | /IP<7:0>             |       |                    |       |  |  |

| bit 7                             |               |                  |                                |                      |       |                    | bit C |  |  |

|                                   |               |                  |                                |                      |       |                    |       |  |  |

| Legend:                           |               |                  |                                |                      |       |                    |       |  |  |

| R = Readable bit W = Writable bit |               | ole bit          | U = Unimplemented, read as '0' |                      |       |                    |       |  |  |

| -n = Value at POR                 |               | '1' = Bit is set |                                | '0' = Bit is cleared |       | x = Bit is unknown |       |  |  |

#### Register 14-4: PxSECMP: Special Event Compare Register

bit 15 **SEVTDIR:** Special Event Trigger Time Base Direction bit<sup>(1)</sup>

1 = A Special Event Trigger will occur when the PWM time base is counting down

0 = A Special Event Trigger will occur when the PWM time base is counting up

bit 14-0 SEVTCMP <14:0>: Special Event Compare Value bit<sup>(2)</sup>

Note 1: SEVTDIR is compared with PTDIR (PxTMR<15>) to generate the Special Event Trigger.

2: SEVTCMP<14:0> is compared with PxTMR<14:0> to generate the Special Event Trigger.

| U-C          | ) U-0                                                                                                                              | U-0                           | U-0                             | R/W-0                                | R/W-0                | R/W-0                | R/W-0                |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|---------------------------------|--------------------------------------|----------------------|----------------------|----------------------|--|--|--|--|

| _            | _                                                                                                                                  |                               |                                 | PMOD4                                | PMOD3                | PMOD2                | PMOD1                |  |  |  |  |

| it 15        |                                                                                                                                    |                               |                                 |                                      |                      |                      | bit 8                |  |  |  |  |

|              | (2)                                                                                                                                | (2)                           | (2)                             | (2)                                  | (2)                  |                      | (2)                  |  |  |  |  |

| R/W-y        |                                                                                                                                    | R/W-y <sup>(2)</sup>          | R/W-y <sup>(2)</sup>            | R/W-y <sup>(2)</sup>                 | R/W-y <sup>(2)</sup> | R/W-y <sup>(2)</sup> | R/W-y <sup>(2)</sup> |  |  |  |  |

| PEN4<br>it 7 | IH PEN3H                                                                                                                           | PEN2H                         | PEN1H                           | PEN4L                                | PEN3L                | PEN2L                | PEN1L                |  |  |  |  |

| 11 7         |                                                                                                                                    |                               |                                 |                                      |                      |                      | bit (                |  |  |  |  |

| egend        | :                                                                                                                                  | y = Bit depen                 | ds on configura                 | ation                                |                      |                      |                      |  |  |  |  |

| -            | adable bit                                                                                                                         | W = Writable                  | 0                               |                                      | mented, read         | as '0'               |                      |  |  |  |  |

| n = Val      | ue at POR                                                                                                                          | '1' = Bit is se               | et                              | '0' = Bit is cle                     |                      | x = Bit is unk       | known                |  |  |  |  |

| t 11-8       | 1 = PWM I/O pin p<br>0 = PWM I/O pin p                                                                                             | air is in the Inde            | pendent Output<br>plementary Ou |                                      |                      |                      |                      |  |  |  |  |

| it 7         | <b>PEN4H:</b> PWMxH4<br>1 = PWMxH4 pin i<br>0 = PWMxH4 pin o                                                                       | s enabled for PV              | ral purpose I/O                 |                                      |                      |                      |                      |  |  |  |  |

| it 6         | PEN3H: PWMxH3 I/O Enable bits <sup>(2)</sup>                                                                                       |                               |                                 |                                      |                      |                      |                      |  |  |  |  |

|              | 1 = PWMxH3 pin i<br>0 = PWMxH3 pin o                                                                                               |                               |                                 | ral purpose I/O                      |                      |                      |                      |  |  |  |  |

| it 5         | PEN2H: PWMxH2 I/O Enable bits <sup>(2)</sup>                                                                                       |                               |                                 |                                      |                      |                      |                      |  |  |  |  |

|              | <ul> <li>1 = PWMxH2 pin is enabled for PWM output</li> <li>0 = PWMxH2 pin disabled; I/O pin becomes general purpose I/O</li> </ul> |                               |                                 |                                      |                      |                      |                      |  |  |  |  |

| it 4         | PEN1H: PWMxH1 I/O Enable bits <sup>(2)</sup>                                                                                       |                               |                                 |                                      |                      |                      |                      |  |  |  |  |

|              | 1 = PWMxH1 pin i<br>0 = PWMxH1 pin o                                                                                               |                               |                                 | ral purpose I/O                      |                      |                      |                      |  |  |  |  |

| it 3         | PEN4L: PWMxL4                                                                                                                      |                               |                                 |                                      |                      |                      |                      |  |  |  |  |

|              | 1 = PWMxL4 pin is<br>0 = PWMxL4 pin c                                                                                              |                               |                                 | ral purpose I/O                      |                      |                      |                      |  |  |  |  |

| it 2         | PEN3L: PWMxL3                                                                                                                      | I/O Enable bits <sup>(2</sup> | 2)                              |                                      |                      |                      |                      |  |  |  |  |

|              | <ul> <li>1 = PWMxL3 pin is enabled for PWM output</li> <li>0 = PWMxL3 pin disabled; I/O pin becomes general purpose I/O</li> </ul> |                               |                                 |                                      |                      |                      |                      |  |  |  |  |

| it 1         | PEN2L: PWMxL2 I/O Enable bits <sup>(2)</sup>                                                                                       |                               |                                 |                                      |                      |                      |                      |  |  |  |  |

|              | <ul> <li>1 = PWMxL2 pin is enabled for PWM output</li> <li>0 = PWMxL2 pin disabled; I/O pin becomes general purpose I/O</li> </ul> |                               |                                 |                                      |                      |                      |                      |  |  |  |  |

| it O         | PEN1L: PWMxL1                                                                                                                      | I/O Enable bits <sup>(2</sup> | 2)                              |                                      |                      |                      |                      |  |  |  |  |

|              | 1 = PWMxL1 pin is<br>0 = PWMxL1 pin c                                                                                              |                               |                                 | ral purpose I/O                      |                      |                      |                      |  |  |  |  |

| Note         | <ol> <li>In devices where<br/>register can be w<br/>PWMxCON1 reg</li> </ol>                                                        | the PWMLOCK                   | Configuration<br>the PWMLOC     | bit is present in<br>CK Configuratio | on bit is asse       | rted (PWMLO          | CK = 1), th          |  |  |  |  |

- PWMLOCK Configuration bit is deasserted (PWMLOCK = 0), the PWMxCON1 register is writable at all times. Refer to 14.16.5 "Write-protected Registers" for further details about the unlock sequence.

2: The Reset condition of the PEN4H:PEN1H and PEN4L:PEN1L bits depends on the value of the PWMPIN device Configuration bit in the FPOR Device Configuration register. When PWMPIN is set to '0' reset values are '1' and when PWMPIN is set to '1' reset values are '0'.

- **3:** The letter "x" in register and pin names refers to the MCPWM module number.

| Register 14-6: | PWMxCON2: PWM Control Register 2 |

|----------------|----------------------------------|

|----------------|----------------------------------|

| U-0       | U-0                                                                                                                                                                                                                                                      | U-0                         | U-0                       | R/W-0          | R/W-0         | R/W-0          | R/W-0 |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------|----------------|---------------|----------------|-------|--|--|

| —         |                                                                                                                                                                                                                                                          | _                           |                           |                | SEVOF         | PS<3:0>        |       |  |  |

| bit 15    |                                                                                                                                                                                                                                                          |                             |                           |                |               |                | bit   |  |  |

|           |                                                                                                                                                                                                                                                          |                             |                           |                |               |                |       |  |  |

| U-0       | U-0                                                                                                                                                                                                                                                      | U-0                         | U-0                       | U-0            | R/W-0         | R/W-0          | R/W-0 |  |  |

|           | —                                                                                                                                                                                                                                                        | —                           |                           | —              | IUE           | OSYNC          | UDIS  |  |  |

| bit 7     |                                                                                                                                                                                                                                                          |                             |                           |                |               |                | bit   |  |  |

| Legend    | :                                                                                                                                                                                                                                                        |                             |                           |                |               |                |       |  |  |

| R = Rea   | idable bit                                                                                                                                                                                                                                               | W = Writable                | e bit                     | U = Unimpl     | emented, read | l as '0'       |       |  |  |

| -n = Valu | ue at POR                                                                                                                                                                                                                                                | '1' = Bit is se             | t                         | '0' = Bit is c | leared        | x = Bit is unk | nown  |  |  |

|           | •<br>0001 = 1:2 postsc:<br>0000 = 1:1 postsc:                                                                                                                                                                                                            | ale                         |                           |                |               |                |       |  |  |

| bit 7-3   | Unimplemented:                                                                                                                                                                                                                                           | Read as '0'                 |                           |                |               |                |       |  |  |

| bit 2     | <b>IUE:</b> Immediate Up<br>1 = Updates to the                                                                                                                                                                                                           | active PxDCy <sup>(1,</sup> | <sup>2)</sup> registers a | re immediate   |               |                |       |  |  |

|           | 0 = Updates to the active PxDCy <sup>(1,2)</sup> registers are synchronized to the PWM time base                                                                                                                                                         |                             |                           |                |               |                |       |  |  |

|           | <b>OSYNC:</b> Output Override Synchronization bit<br>1 = Output overrides via the PxOVDCON <sup>(1)</sup> register are synchronized to the PWM time base<br>0 = Output overrides via the PxOVDCON <sup>(1)</sup> register occur on the next Tcy boundary |                             |                           |                |               |                |       |  |  |

| bit 1     |                                                                                                                                                                                                                                                          |                             |                           |                |               |                |       |  |  |

**Note 1:** The letter "x" refers to the MCPWM module number.

2: The letter "y" refers to the MCPWM Duty Cycle register number.

| R/W-0             | R/W-0   | R/W-0            | R/W-0 | R/W-0                              | R/W-0                          | R/W-0 | R/W-0 |

|-------------------|---------|------------------|-------|------------------------------------|--------------------------------|-------|-------|

| DTBP              | 'S<1:0> |                  |       | DTB<5                              | :0>                            |       |       |

| bit 15            |         |                  |       |                                    |                                |       | bit 8 |

| R/W-0             | R/W-0   | R/W-0            | R/W-0 | R/W-0                              | R/W-0                          | R/W-0 | R/W-0 |

| DTAPS<1:0>        |         |                  |       |                                    |                                |       |       |

| bit 7             | bit 7   |                  |       |                                    |                                |       | bit 0 |

| Legend:           |         |                  |       |                                    |                                |       |       |

| R = Readable bit  |         | W = Writable     | e bit | U = Unimpler                       | U = Unimplemented, read as '0' |       |       |

| -n = Value at POR |         | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is ur |                                |       | nown  |

| Register 14-7: | PxDTCON1: Dead Time Control Register 1 |

|----------------|----------------------------------------|

|----------------|----------------------------------------|

bit 15-14 DTBPS<1:0>: Dead Time Unit B Prescale Select bits

11 = Clock period for Dead Time Unit B is 8 Tcy

10 = Clock period for Dead Time Unit B is 4 TCY

01 = Clock period for Dead Time Unit B is 2 TCY

00 = Clock period for Dead Time Unit B is TCY

bit 13-8 DTB<5:0>: Unsigned 6-bit Dead Time Value bits for Dead Time Unit B

bit 7-6 DTAPS<1:0>: Dead Time Unit A Prescale Select bits

11 = Clock period for Dead Time Unit A is 8 TCY

10 = Clock period for Dead Time Unit A is 4 Tcy

01 = Clock period for Dead Time Unit A is 2 TCY

00 = Clock period for Dead Time Unit A is TCY

bit 5-0 **DTA<5:0>:** Unsigned 6-bit Dead Time Value bits for Dead Time Unit A

14

Motor Contro PWM

| bit 15<br>R/W-0<br>DTS4A<br>bit 7<br>Legend: | R/W-0<br>DTS4I                                                                                     | R/W-0<br>DTS3A   |              | —               | —            | _              | —     |  |  |  |  |

|----------------------------------------------|----------------------------------------------------------------------------------------------------|------------------|--------------|-----------------|--------------|----------------|-------|--|--|--|--|

| R/W-0<br>DTS4A<br>bit 7                      | 1                                                                                                  |                  | R/W-0        |                 |              |                |       |  |  |  |  |

| DTS4A<br>bit 7                               | 1                                                                                                  |                  | R/W-0        |                 |              |                | bit 8 |  |  |  |  |

| DTS4A<br>bit 7                               | 1                                                                                                  |                  | FV/VV-0      | R/W-0           | R/W-0        | R/W-0          | R/W-0 |  |  |  |  |

| bit 7                                        | 01041                                                                                              | DIGGA            | DTS3I        | DTS2A           | DTS2I        | DTS1A          | DTS1I |  |  |  |  |

| l egend:                                     |                                                                                                    |                  | DTSSI        | DIGZA           | 01321        | DISIA          | bit ( |  |  |  |  |

|                                              |                                                                                                    |                  |              |                 |              |                |       |  |  |  |  |

| R = Reada                                    | able bit                                                                                           | W = Writable     | bit          | U = Unimple     | mented, read | as '0'         |       |  |  |  |  |

| -n = Value                                   |                                                                                                    | '1' = Bit is se  |              | '0' = Bit is cl |              | x = Bit is unk | nown  |  |  |  |  |

|                                              |                                                                                                    |                  |              |                 |              |                |       |  |  |  |  |

| bit 15-8                                     | Unimplemented: R                                                                                   | Read as '0'      |              |                 |              |                |       |  |  |  |  |

| bit 7                                        | DTS4A: Dead Time Select bit for PWM4 Signal Going Active                                           |                  |              |                 |              |                |       |  |  |  |  |

|                                              | <ul> <li>1 = Dead time provided from Unit B</li> <li>0 = Dead time provided from Unit A</li> </ul> |                  |              |                 |              |                |       |  |  |  |  |

|                                              | •                                                                                                  |                  |              |                 |              |                |       |  |  |  |  |

|                                              | DTS4I: Dead Time                                                                                   |                  | •            | oing Inactive   |              |                |       |  |  |  |  |

|                                              | <ol> <li>Dead time provided from Unit B</li> <li>Dead time provided from Unit A</li> </ol>         |                  |              |                 |              |                |       |  |  |  |  |

|                                              | DTS3A: Dead Time Select bit for PWM3 Signal Going Active                                           |                  |              |                 |              |                |       |  |  |  |  |

|                                              | 1 = Dead time provided from Unit B                                                                 |                  |              |                 |              |                |       |  |  |  |  |

|                                              | 0 = Dead time provided from Unit A                                                                 |                  |              |                 |              |                |       |  |  |  |  |

| bit 4                                        | DTS3I: Dead Time Select bit for PWM3 Signal Going Inactive                                         |                  |              |                 |              |                |       |  |  |  |  |

|                                              | 1 = Dead time provided from Unit B                                                                 |                  |              |                 |              |                |       |  |  |  |  |

|                                              | 0 = Dead time provi                                                                                |                  |              |                 |              |                |       |  |  |  |  |

|                                              | DTS2A: Dead Time Select bit for PWM2 Signal Going Active                                           |                  |              |                 |              |                |       |  |  |  |  |

|                                              | <ol> <li>Dead time provided from Unit B</li> <li>Dead time provided from Unit A</li> </ol>         |                  |              |                 |              |                |       |  |  |  |  |

|                                              | Dead time provided from Onit A<br>DTS2I: Dead Time Select bit for PWM2 Signal Going Inactive       |                  |              |                 |              |                |       |  |  |  |  |

|                                              | 1 = Dead time provi                                                                                |                  | •            |                 |              |                |       |  |  |  |  |

|                                              | <ul> <li>Dead time provi</li> <li>Dead time provi</li> </ul>                                       |                  |              |                 |              |                |       |  |  |  |  |

| bit 1                                        | DTS1A: Dead Time                                                                                   | Select bit for P | WM1 Signal G | oing Active     |              |                |       |  |  |  |  |

|                                              | 1 = Dead time provi                                                                                |                  |              |                 |              |                |       |  |  |  |  |

|                                              | 0 = Dead time provi                                                                                |                  |              |                 |              |                |       |  |  |  |  |

|                                              | DTS1I: Dead Time                                                                                   |                  | •            | oing Inactive   |              |                |       |  |  |  |  |

|                                              | <ul><li>1 = Dead time provi</li><li>0 = Dead time provi</li></ul>                                  |                  |              |                 |              |                |       |  |  |  |  |

| R/W-0             | R/W-0                                                                                                                                                | R/W-0                                              | R/W-0                                            | R/W-0                            | R/W-0                       | R/W-0                  | R/W-0                        |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|--------------------------------------------------|----------------------------------|-----------------------------|------------------------|------------------------------|--|--|--|

| FAOV4H            | H FAOV4L                                                                                                                                             | FAOV3H                                             | FAOV3L                                           | FAOV2H                           | FAOV2L                      | FAOV1H                 | FAOV1L                       |  |  |  |

| bit 15            | <b>_</b>                                                                                                                                             |                                                    |                                                  |                                  |                             |                        | bit 8                        |  |  |  |

|                   |                                                                                                                                                      |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

| R/W-0             | U-0                                                                                                                                                  | U-0                                                | U-0                                              | R/W-y <sup>(3)</sup>             | R/W-y <sup>(3)</sup>        | R/W-y <sup>(3)</sup>   | R/W-y <sup>(3)</sup>         |  |  |  |

| FLTAM             |                                                                                                                                                      |                                                    |                                                  | FAEN4 <sup>(4)</sup>             | FAEN3 <sup>(4)</sup>        | FAEN2 <sup>(4)</sup>   | FAEN1 <sup>(4)</sup>         |  |  |  |

| bit 7             |                                                                                                                                                      |                                                    |                                                  |                                  |                             |                        | bit 0                        |  |  |  |

|                   |                                                                                                                                                      |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

| Legend:           |                                                                                                                                                      | y = Bit depen                                      | ds on configura                                  | ation                            |                             |                        |                              |  |  |  |

| R = Reada         | able bit                                                                                                                                             | W = Writable                                       | bit                                              | U = Unimple                      | mented, read                | as '0'                 |                              |  |  |  |

| -n = Value at POR |                                                                                                                                                      | '1' = Bit is se                                    | t                                                | '0' = Bit is cle                 | eared                       | x = Bit is unl         | known                        |  |  |  |

|                   |                                                                                                                                                      |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

| bit 15-8 I        | FAOV4H:FAOV1L:                                                                                                                                       | Fault Input A P                                    | WM Override '                                    | Value bits                       |                             |                        |                              |  |  |  |

|                   | 1 = PWM output pir                                                                                                                                   | -                                                  |                                                  |                                  | ent                         |                        |                              |  |  |  |

|                   | 0 = PWM output pir                                                                                                                                   |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

| bit 7 I           | FLTAM: Fault A Mo                                                                                                                                    | de bit                                             |                                                  |                                  |                             |                        |                              |  |  |  |

|                   | 1 = Fault A input pir                                                                                                                                |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

| (                 | 0 = Fault A input pir                                                                                                                                | n latches all cor                                  | trol pins to the                                 | e programmed s                   | tates in PxFL               | .TACON<15:8>           | •                            |  |  |  |

| bit 6-4           | Unimplemented: R                                                                                                                                     | Read as '0'                                        |                                                  |                                  |                             |                        |                              |  |  |  |

| bit 3 I           | FAEN4: Fault Input A Enable bit <sup>(3,4)</sup>                                                                                                     |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

|                   | 1 = PWMxH4/PWMxL4 pin pair is controlled by Fault Input A                                                                                            |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

|                   | 0 = PWMxH4/PWMxL4 pin pair is not controlled by Fault Input A                                                                                        |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

|                   | FAEN3: Fault Input A Enable bit <sup>(3,4)</sup>                                                                                                     |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

|                   | 1 = PWMxH3/PWMxL3 pin pair is controlled by Fault Input A                                                                                            |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

|                   | 0 = PWMxH3/PWMxL3 pin pair is not controlled by Fault Input A                                                                                        |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

|                   | FAEN2: Fault Input A Enable bit <sup>(3,4)</sup>                                                                                                     |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

|                   | <ul> <li>1 = PWMxH2/PWMxL2 pin pair is controlled by Fault Input A</li> <li>0 = PWMxH2/PWMxL2 pin pair is not controlled by Fault Input A</li> </ul> |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

|                   |                                                                                                                                                      |                                                    |                                                  | by Fault Input A                 |                             |                        |                              |  |  |  |

|                   | <b>FAEN1:</b> Fault Input A Enable bit <sup>(3,4)</sup><br>1 = PWMxH1/PWMxL1 pin pair is controlled by Fault Input A                                 |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

|                   | 0 = PWMxH1/PWM                                                                                                                                       |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

|                   |                                                                                                                                                      |                                                    |                                                  | y r aan mpar r                   |                             |                        |                              |  |  |  |

| Noto 1:           | In devices where t                                                                                                                                   |                                                    | Configuration                                    | hit is present in                | the EASCS                   | El configuratio        | n register this              |  |  |  |

| note n            | register can be wr                                                                                                                                   |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

|                   | PxFLTACON regis                                                                                                                                      |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

|                   |                                                                                                                                                      | ouration bit is d                                  | easserted (PV                                    | VMLOCK = 0),                     | the PxFLTAC                 | ON register is         | writable at all              |  |  |  |

|                   | PWMLOCK Config                                                                                                                                       |                                                    |                                                  |                                  |                             |                        |                              |  |  |  |

|                   | times. Refer to 14                                                                                                                                   | .16.5 "Write-pr                                    | otected Regis                                    |                                  |                             |                        |                              |  |  |  |

| 2:                |                                                                                                                                                      | .16.5 "Write-pr                                    | otected Regis                                    |                                  |                             |                        |                              |  |  |  |

|                   | times. Refer to 14                                                                                                                                   | .16.5 "Write-pr<br>gister and pin n<br>the PWMLOCK | otected Regis<br>ames refers to<br>Configuration | the MCPWM n<br>bit is present in | nodule number<br>the FOSCSE | er.<br>EL Configuratic | equence.<br>on register, the |  |  |  |

**4:** The Fault pin A has priority over Fault pin B, if enabled.

1 Motor Control PWM

| Register  | 14-10:                                                                                                                                                                   | PxFLTBCO                                       | N: Fault B Con                                                                                | trol Register <sup>(1</sup>                      | ,4)                                                |                                                  |                                             |                                                    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------|----------------------------------------------------|--------------------------------------------------|---------------------------------------------|----------------------------------------------------|

| R/W-      | 0                                                                                                                                                                        | R/W-0                                          | R/W-0                                                                                         | R/W-0                                            | R/W-0                                              | R/W-0                                            | R/W-0                                       | R/W-0                                              |

| FBOV4     | 4H                                                                                                                                                                       | FBOV4L                                         | FBOV3H                                                                                        | FBOV3L                                           | FBOV2H                                             | FBOV2L                                           | FBOV1H                                      | FBOV1L                                             |

| bit 15    |                                                                                                                                                                          |                                                |                                                                                               |                                                  |                                                    |                                                  |                                             | bit 8                                              |

| R/W-      | 0                                                                                                                                                                        | U-0                                            | U-0                                                                                           | U-0                                              | R/W-y <sup>(3)</sup>                               | R/W-y <sup>(3)</sup>                             | R/W-y <sup>(3)</sup>                        | R/W-y <sup>(3)</sup>                               |

| FLTB      |                                                                                                                                                                          | _                                              | _                                                                                             | _                                                | FBEN4 <sup>(4)</sup>                               | FBEN3 <sup>(4)</sup>                             | FBEN2 <sup>(4)</sup>                        | FBEN1 <sup>(4)</sup>                               |

| bit 7     |                                                                                                                                                                          |                                                |                                                                                               |                                                  |                                                    |                                                  |                                             | bit (                                              |

| Legend:   |                                                                                                                                                                          |                                                | v – Dit dopon                                                                                 | nds on configura                                 | ation                                              |                                                  |                                             |                                                    |

| R = Rea   |                                                                                                                                                                          | t                                              | y – ыт deper<br>W = Writable                                                                  | •                                                |                                                    | mented, read                                     | as '0'                                      |                                                    |

| -n = Valu |                                                                                                                                                                          |                                                | '1' = Bit is se                                                                               |                                                  | 0' = Bit is cl                                     |                                                  | x = Bit is unl                              | (00)(0                                             |

|           |                                                                                                                                                                          | νn                                             |                                                                                               | 51                                               |                                                    | ealeu                                            |                                             |                                                    |

| hit 7     | <ul> <li>1 = PWM output pin is driven Active on an external fault input event</li> <li>0 = PWM output pin is driven Inactive on an external fault input event</li> </ul> |                                                |                                                                                               |                                                  |                                                    |                                                  |                                             |                                                    |

| bit 7     | FLTBM: Fault B Mode bit                                                                                                                                                  |                                                |                                                                                               |                                                  |                                                    |                                                  |                                             |                                                    |

|           |                                                                                                                                                                          |                                                | n functions in C<br>n latches all coi                                                         |                                                  |                                                    | tatas in DvEl <sup>-</sup>                       |                                             |                                                    |

| bit 6-4   |                                                                                                                                                                          | plemented: F                                   |                                                                                               |                                                  | programmed s                                       |                                                  |                                             | •                                                  |

| bit 3     |                                                                                                                                                                          |                                                | t B Enable bit <sup>(3,</sup>                                                                 | 4)                                               |                                                    |                                                  |                                             |                                                    |

| DIL S     |                                                                                                                                                                          |                                                | IxL4 pin pair is                                                                              |                                                  | ault Input B                                       |                                                  |                                             |                                                    |

|           |                                                                                                                                                                          |                                                | 1xL4 pin pair is                                                                              |                                                  | y Fault Input B                                    |                                                  |                                             |                                                    |

| bit 2     |                                                                                                                                                                          |                                                | t B Enable bit <sup>(3,</sup>                                                                 |                                                  |                                                    |                                                  |                                             |                                                    |

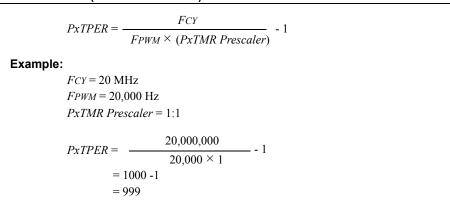

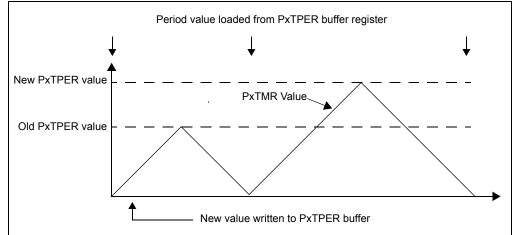

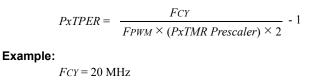

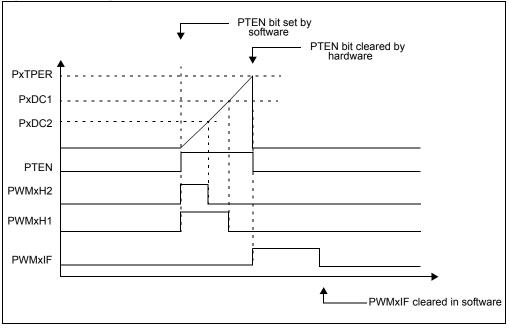

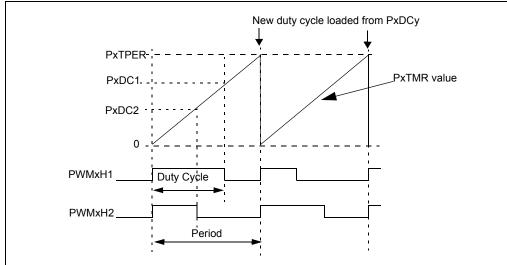

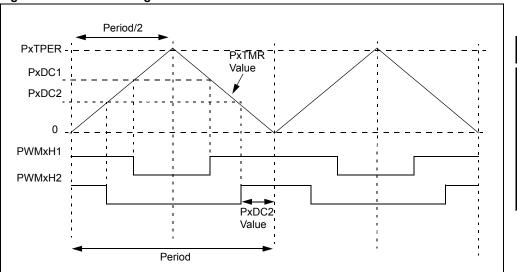

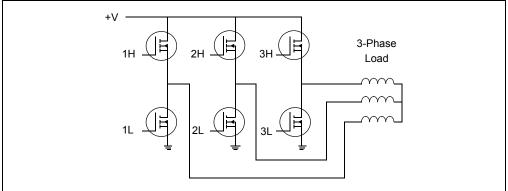

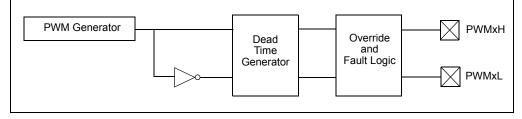

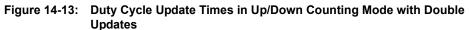

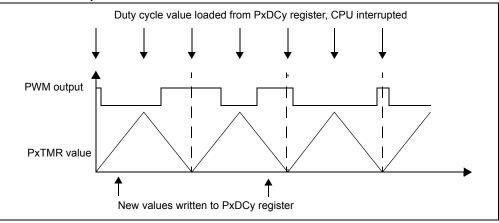

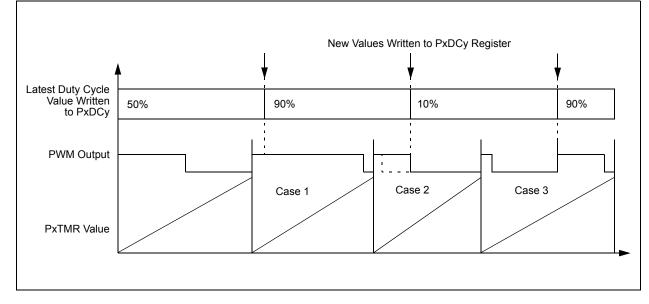

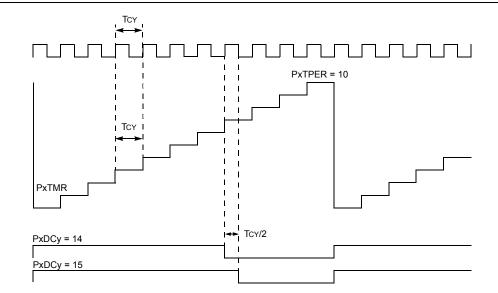

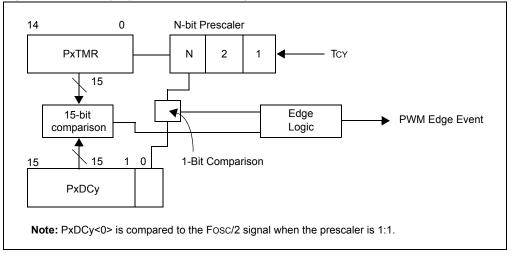

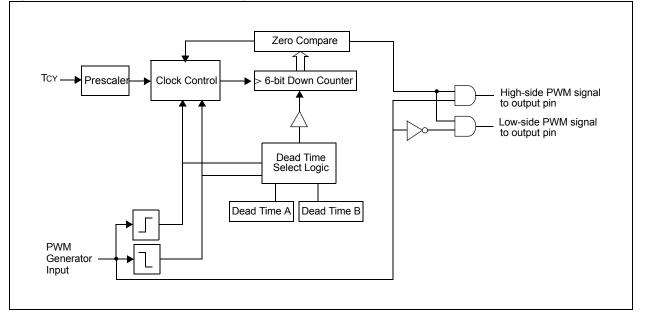

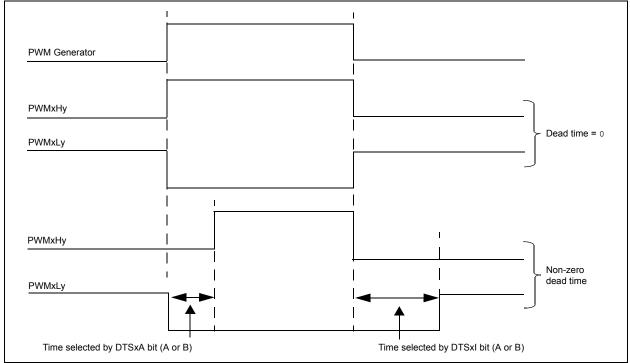

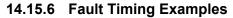

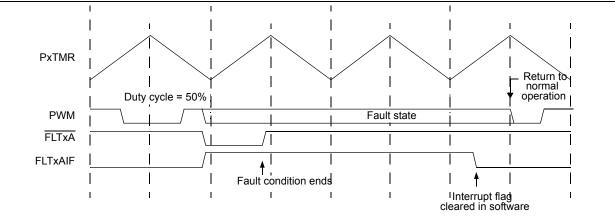

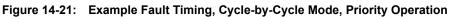

|           |                                                                                                                                                                          |                                                | IxL3 pin pair is<br>IxL3 pin pair is                                                          |                                                  |                                                    |                                                  |                                             |                                                    |