# Section 12. Input Capture

# HIGHLIGHTS

This section of the manual contains the following major topics:

| 12.1  | Introduction                                  |       |

|-------|-----------------------------------------------|-------|

| 12.2  | Input Capture Registers                       |       |

| 12.3  | Capture Event Generation                      |       |

| 12.4  | Capture Buffer Operation                      |       |

| 12.5  | Input Capture Interrupts                      |       |

| 12.6  | Input Capture Operation in Power-Saving Modes | 12-11 |

| 12.7  | I/O Pin Control                               | 12-11 |

| 12.8  | Register Maps                                 |       |

| 12.9  | Design Tips                                   |       |

| 12.10 | Related Application Notes                     |       |

| 12.11 | Revision History                              |       |

# 12.1 INTRODUCTION

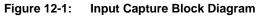

This section describes the Input Capture module and its associated operational modes. The Input Capture module is used to capture a timer value from one of the two selectable time bases upon an event on an input pin. The Input Capture features are quite useful in applications that require frequency (time period) and pulse measurement. Figure 12-1 depicts a simplified block diagram of the Input Capture module.

The Input Capture module has multiple operating modes. The operating modes are selected via the Input Capture Control (ICxCON) register and include:

- Capture timer value on every falling edge of the input applied at the ICx pin

- Capture timer value on every rising edge of the input applied at the ICx pin

- Capture timer value on every 4th rising edge of the input applied at the ICx pin

- Capture timer value on every 16th rising edge of the input applied at the ICx pin

- Capture timer value on every rising and every falling edge of the input applied at the ICx pin

- Device wake-up from Sleep and Idle mode on the rising edge of the input applied at the ICx pin

The Input Capture module has a four level First-In First-Out (FIFO) buffer. The user-assigned application can select the number of capture events required to generate a CPU interrupt.

**Note:** Each dsPIC33F device variant has one or more Input Capture modules. An 'x' used in the names of pins, control/status bits and registers denotes the particular Input Capture module number. Refer to the specific device data sheets for more details.

# 12.2 INPUT CAPTURE REGISTERS

Each capture channel available on dsPIC33F family devices has these registers:

- ICxCON: Input Capture Control register

- ICxBUF: Input Capture Buffer register

#### Register 12-1: ICxCON: Input Capture x Control Register

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|--------|-----|-----|-----|-----|-------|

| —      | —   | ICSIDL | —   | —   | —   | —   | —     |

| bit 15 |     |        |     |     |     |     | bit 8 |

| R/W-0 | R/W-0    | R/W-0 | R-0, HC | R-0, HC | R/W-0 | R/W-0 | R/W-0 |

|-------|----------|-------|---------|---------|-------|-------|-------|

| ICTMR | ICI<1:0> |       | ICOV    | ICBNE   |       |       |       |

| bit 7 |          |       |         |         |       |       | bit 0 |

| Legend:           | HC = Cleared in Hardware |                             |                    |

|-------------------|--------------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read | as '0'             |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared        | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                                                                              |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | ICSIDL: Input Capture x Stop in Idle Control bit                                                                                                                                                                                        |

|           | 1 = Input capture halts in CPU Idle mode                                                                                                                                                                                                |

|           | 0 = Input capture continues to operate in CPU Idle mode                                                                                                                                                                                 |

| bit 12-8  | Unimplemented: Read as '0'                                                                                                                                                                                                              |

| bit 7     | ICTMR: Input Capture x Timer Select bit                                                                                                                                                                                                 |

|           | <ul> <li>1 = TMR2 contents are captured on capture event</li> <li>0 = TMR3 contents are captured on capture event</li> </ul>                                                                                                            |

| bit 6-5   | ICI<1:0>: Select Number of Captures per Interrupt bits                                                                                                                                                                                  |

|           | 11 = Interrupt on every fourth capture event                                                                                                                                                                                            |

|           | 10 = Interrupt on every third capture event                                                                                                                                                                                             |

|           | <ul><li>01 = Interrupt on every second capture event</li><li>00 = Interrupt on every capture event</li></ul>                                                                                                                            |

| bit 4     | ICOV: Input Capture x Overflow Status Flag bit (read-only)                                                                                                                                                                              |

| bit i     | 1 = Input capture overflow occurred                                                                                                                                                                                                     |

|           | 0 = No input capture overflow occurred                                                                                                                                                                                                  |

| bit 3     | ICBNE: Input Capture x Buffer Empty Status Flag bit (read-only)                                                                                                                                                                         |

|           | <ul> <li>1 = Input capture buffer is not empty, at least one more capture value can be read</li> <li>0 = Input capture buffer is empty</li> </ul>                                                                                       |

| bit 2-0   | ICM<2:0>: Input Capture x Mode Select bits                                                                                                                                                                                              |

|           | <ul> <li>111 = Input capture functions as interrupt pin only when device is in Sleep or Idle mode (rising edge detect only, all other control bits are not applicable)</li> <li>110 = Unused (Input Capture module disabled)</li> </ul> |

|           | 101 = Capture mode, every 16th rising edge                                                                                                                                                                                              |

|           | 100 = Capture mode, every 4th rising edge                                                                                                                                                                                               |

|           | 011 = Capture mode, every rising edge<br>010 = Capture mode, every falling edge                                                                                                                                                         |

|           | <ul> <li>010 = Capture mode, every raining edge</li> <li>001 = Capture mode, every edge – rising and falling (ICI&lt;1:0&gt; bits do not control interrupt generation for this mode)</li> </ul>                                         |

|           | 000 = Input Capture module turned off                                                                                                                                                                                                   |

|           |                                                                                                                                                                                                                                         |

12

# 12.3 CAPTURE EVENT GENERATION

## 12.3.1 Timer Selection

Each dsPIC33F family device has one or more input capture channels. Each channel can select between Timer2 and Timer3 for its time base. Selection of the timer resource is accomplished through the Input Capture Timer Select (ICTMR) bit in the Input Capture Control (ICxCON<7>) register. This timer can be set using the internal clock source (Fosc/2), or an external clock source applied at the TxCK pin.

## 12.3.2 Input Capture Event Modes

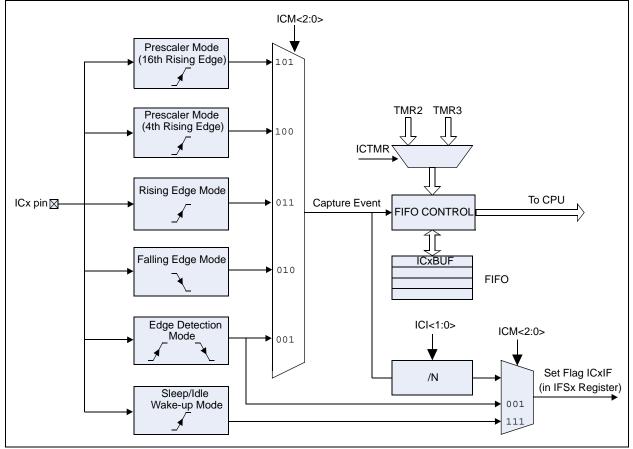

The Input Capture module captures the 16-bit value of the selected timer (Timer2 or Timer3), when a capture event occurs. A capture event is defined as a write of a timer value into the capture buffer.

The Input Capture modes are configured by setting the appropriate Input Capture Mode (ICM<2:0>) bits in the Input Capture Control (ICxCON<2:0>) register. Table 12-1 lists the Input Capture mode and capture events for the different bit settings. The user-assigned application must disable the Input Capture module (i.e., ICM<2:0> = 000) before changing a Capture mode. Figure 12-2 illustrates the capture events for various Capture modes.

Table 12-1:

Input Capture Modes

| ICM<2:0><br>Value | Input Capture Mode             | Capture Event Generation                                    |

|-------------------|--------------------------------|-------------------------------------------------------------|

| 000               | Module disabled                | _                                                           |

| 001               | Edge Capture mode              | On both rising and falling edge of the capture input signal |

| 010               | Falling Edge mode              | On the falling edge of the capture input signal             |

| 011               | Rising Edge mode               | On the rising edge of the capture input signal              |

| 100               | Prescaler mode (divided by 4)  | On every 4th rising edge of the capture input signal        |

| 101               | Prescaler mode (divided by 16) | On every 16th rising edge of the capture input signal       |

| 110               | Unused (module disabled)       | _                                                           |

| 111               | Sleep/Idle Wake-up mode        | No capture event                                            |

**Note 1:** The Input Capture (ICx) pin has minimum high time and low time specifications. Refer to the specific device data sheet for more details.

**2:** The latency from the time the transition happens at the ICx pin to the time the capture event is generated is two instruction cycles.

12

# 12.4 CAPTURE BUFFER OPERATION

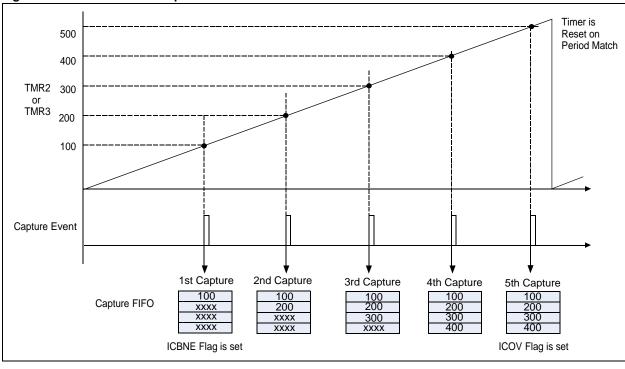

The Input Capture module can select Timer2 or Timer3 as its time base. The selected timer value is captured and stored in a four deep FIFO buffer on every capture event as shown in Figure 12-3. The ICxBUF register provides access to the FIFO buffer as it is memory mapped.

Two status flags are associated with the FIFO buffer:

- Input Capture x Buffer Empty Status (ICBNE) flag

- Input Capture x Overflow Status (ICOV) flag

These status flags are cleared:

- On any device Reset

- When the module is disabled by the Input Capture Mode Selection (ICM<2:0>) bits

#### 12.4.1 Input Capture Buffer Not Empty (ICBNE)

The ICBNE read-only status bit (ICxCON<3>) is set on the first input capture event and remains set until all capture events are read from the capture buffer. For example, if three capture events occur, then three reads of the capture buffer are required before the ICBNE (ICxCON<3>) bit is cleared. Similarly, if four capture events occur, four reads are required to clear the bit. Each read of the capture buffer allows the remaining word(s) to move to the next available top location.

## 12.4.2 Input Capture Overflow (ICOV)

The ICOV read-only status bit (ICxCON<4>) is set when the capture buffer overflows. If the event that the buffer is full with four capture events, and a fifth capture event takes place before the buffer is read, an overrun condition occurs, and the ICOV (ICxCON<4>) bit is set to logic '1'.

To clear the overrun condition, the capture buffer must be read four times. On the fourth read, the ICOV (ICxCON<4>) status flag is cleared. The capture event does not write timer values into the FIFO buffer when it is full.

**Note 1:** The latency from the time the transition happens at the capture input (ICx pin) to the time the capture event is generated is two instruction cycles.

2: The Overflow flag remains cleared in Edge Detect mode (ICM = 0b001).

# 12.5 INPUT CAPTURE INTERRUPTS

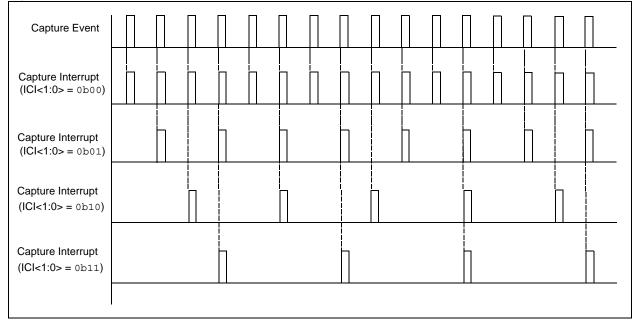

The input capture channel can generate an interrupt based on the selected number of capture events, as illustrated in Figure 12-4. The number of events is set by the Input Capture Interrupt (ICI<1:0>) bits in the Capture Control (ICxCON<6:5>) register, as provided in Table 12-2. The user-assigned application must disable the Input Capture module (ICM<2:0> = 000) before changing the ICI<1:0> bits.

When the capture interrupt is generated on every capture event (ICI<1:0> = 00), the FIFO overflow condition does not inhibit the capture interrupt. If the capture interrupt is not generated on every capture event, the FIFO overflow condition inhibits the capture interrupt. Therefore, all the captured values must be read from the capture buffer on every capture interrupt. For example, if the capture interrupt is generated on every second capture event (ICI = 01), the capture buffer must be read twice. Similarly, if the capture interrupt is generated on every third capture event (ICI = 10), the capture buffer must be read three times.

**Note:** In Edge Detection Mode (ICM = 001), the interrupt is generated on every capture event and the Input Capture Interrupt (ICI<1:0>) bits are ignored.

| ICI<1:0> Values | Input Capture Interrupt Generation      |

|-----------------|-----------------------------------------|

| 00              | Interrupt on every capture event        |

| 01              | Interrupt on every second capture event |

| 10              | Interrupt on every third capture event  |

| 11              | Interrupt on every fourth capture event |

#### Table 12-2: Input Capture Interrupt Selection

| Figure 12-4: | Input Capture Interrupt Generation |

|--------------|------------------------------------|

|              |                                    |

Note: Each Input Capture channel has interrupt flag status bits (ICxIF), Interrupt Enable bits (ICxIE) and Interrupt Priority Control bits (ICxIP<2:0>). Refer to Section 6. "Interrupts" (DS70184) in the "*dsPIC33F Family Reference Manual*" for more details on peripheral interrupts.

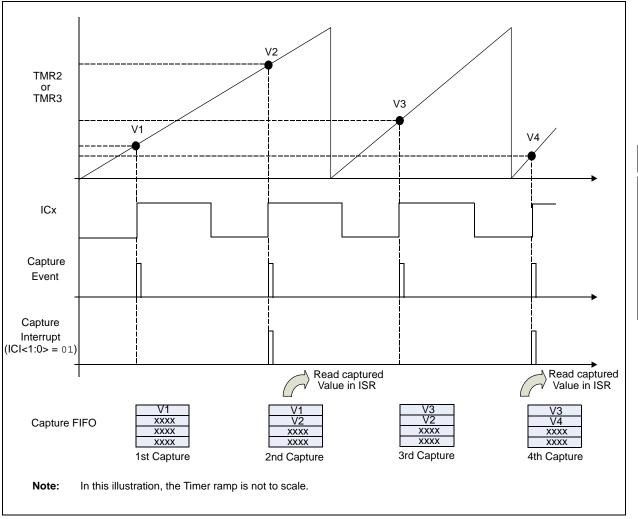

#### 12.5.1 Code Example for Period Measurement

The following code example shows the time period measurement using the Input Capture module. The capture event is generated on every rising edge and the capture interrupt is generated after taking two time stamps for period measurement, as illustrated in Figure 12-5.

Example 12-1: Capture Code Example

```

// Initialize Capture Module

IC1CONbits.ICM=0b00;

// Disable Input Capture 1 module

IC1CONbits.ICTMR= 1;

// Select Timer2 as the IC1 Time base

IC1CONbits.ICI= 0b01;

// Interrupt on every second capture event

IC1CONbits.ICM= 0b011;

// Generate capture event on every Rising edge

// Enable Capture Interrupt And Timer2

// Setup IC1 interrupt priority level

IPCObits.IC1IP = 1;

IFSObits.IC1IF = 0;

// Clear IC1 Interrupt Status Flag

IECObits.IC1IE = 1;

// Enable IC1 interrupt

// Capture Interrupt Service Routine

unsigned int timePeriod= 0;

void __attribute__((__interrupt__)) _IC1Interrupt(void)

unsigned int t1,t2;

t1=IC1BUF;

t2=IC1BUF;

IFSObits.IC1IF=0;

if(t2>t1)

timePeriod = t2-t1;

else

timePeriod = (PR2 - t1) + t2;

```

12

Input Capture

## 12.5.2 Input Capture Operation with DMA

Some dsPIC33F family devices include a Direct Memory Access (DMA) module, which allows data to be transferred from the Input Capture module to data memory without CPU intervention. Refer to the specific dsPIC33F device data sheet to see if DMA exists on your particular device. Refer to **Section 22.** "Direct Memory Access (DMA)" (DS70182) in the "*dsPIC33F Family Reference Manual*" for more details on the DMA module.

When the Input Capture module and DMA channel are appropriately configured, the Input Capture module issues a DMA request for every capture event. The DMA transfers data from the Input Capture Buffer (ICxBUF) register into RAM, and issues a CPU interrupt after a predefined number of transfers.

The DMA channel must be initialized with the following:

- The DMA Request Source Selection (IRQSEL<6:0>) bits in the DMA Request (DMAxREQ<6:0>) register must select the DMA transfer request from Input Capture module

- The DMA Channel Peripheral Address (DMAxPAD) register must be initialized with the address of the Input Capture Buffer (ICxBUF) register

- The Transfer Direction (DIR) bit in DMA Control (DMAxCON<13>) register must be cleared. In this condition, data is read from the peripheral and written to the dual port DMA memory

In addition, the input capture interrupt bits must be cleared (ICI < 1:0 > = 0.0) to generate DMA request for every capture event.

Example 12-2 provides sample code that transfers the capture values to RAM with DMA.

DMA Channel 0 is set up for the Input Capture module with the following configuration:

- Transfer data from the Input Capture module to RAM

- · One-shot operating mode

- Register Indirect with Post-Increment addressing

- · Single buffer

- 256 transfers per buffer

- Transfer words

#### Example 12-2: Input Capture with DMA

```

// Initialize Capture module

IC1CONbits.ICM = 0b00;

// Disable Input Capture 1 module

IC1CONbits.ICTMR = 1;

// Select Timer2 as the IC1 Time base

ICICONDITS.ICIMR = 1;// Select Inmer2 as the ICI Inme DaseICICONDits.ICI = 0b00;// Interrupt on every second capture eventICICONDits.ICM = 0b001;// Generate capture event on every Rising edge

Setup DMA for Input Capture:

// Define Buffer in DMA RAM

unsigned int BufferA[256] attribute ((space(dma)));

// Register indirect

// One Shot, Ping-Por

// Peripheral to RAM

// Address of the cap

DMA0CONbits.AMODE = 0b00;

// Register indirect with post increment

// One Shot, Ping-Pong mode Disabled

DMA0CONbits.MODE = 0b01;

DMA0CONbits.DIR = 0;

DMAOPAD = (int) \& IC1BUF;

// Address of the capture buffer register

DMAOREQ = 1;// Select IC module as DMA request source

// Number of words to buffer

DMAOCNT = 255;

DMA0STA = builtin dmaoffset(&BufferA);

IFSObits.DMAOIF = 0;

// Clear the DMA interrupt flag bit

IECObits.DMAOIE = 1;

// Enable DMA interrupt enable bit

DMA0CONbits.CHEN = 1;

Setup DMA Interrupt Handler

void __attribute__((__interrupt__)) _DMA0Interrupt(void)

// Process the captured values

IFSObits.DMA0IF = 0;

// Clear the DMA0 Interrupt Flag

}

```

#### 12.5.3 Capture Pin as External Interrupt

The Input Capture (ICx) pin can be used as an auxiliary external interrupt source by clearing the Input Capture Interrupt (ICI = 00) bits. In this condition an interrupt is generated on every capture event, and the FIFO overflow condition does not inhibit the capture interrupt. Consequently, the input capture buffer need not be read in the Capture Interrupt Service Routine (ISR). The Input Capture Mode (ICM<2:0>) bits can be used to select the edge polarity for the interrupt.

# 12.6 INPUT CAPTURE OPERATION IN POWER-SAVING MODES

## 12.6.1 Input Capture Operation in Sleep Mode

The Input Capture module does not operate when the device is in Sleep mode. In Sleep mode, the Input Capture (ICx) pin can only function as an external interrupt source for wake-up. The Sleep mode is enabled by setting the Input Capture Mode bits (ICM<2:0> = 111). In this mode, if the input capture interrupt is enabled, a rising edge on the capture pin generates capture interrupt.

The capture interrupt wakes up the device from Sleep, and the following occurs:

- If the assigned priority for the interrupt is less than, or equal, to the current CPU priority, the device wakes up and continues code execution from the instruction following the PWRSAV instruction that initiated Sleep mode.

- If the assigned priority level for the interrupt source is greater than the current CPU priority, the device wakes up and the CPU exception process begins. Code execution continues from the first instruction of the capture ISR.

## 12.6.2 Input Capture Operation in Idle Mode

When the device enters Idle mode, the system clock sources remain functional and the CPU stops executing code. The Input Capture Stop-in Idle (ICSIDL) bit selection in the Input Capture Control (ICxCON<13>) register determines whether the module stops in Idle mode or continues to operate in Idle mode.

If ICSIDL = 0 (ICxCON<13>), the module continues to operate in Idle mode providing full functionality of the Input Capture module including the 4:1 and 16:1 prescaler capture settings. The prescaler capture settings are defined by control bits ICM<2:0> (ICxCON<2:0>). These modes require that the selected timer is enabled during Idle mode as well.

If ICSIDL = 1 (ICxCON<13>), the module stops in Idle mode. The module performs the same functions as Sleep mode, when stopped in Idle mode. Refer to **12.6.1** "**Input Capture Operation in Sleep Mode**".

# 12.7 I/O PIN CONTROL

When the Input Capture module is enabled, the user-assigned application must ensure that the I/O pin direction is configured for an input by setting the associated TRIS bit. The pin direction is not set when the Input Capture module is enabled. All other peripherals multiplexed with the input pin must be disabled.

# 12.8 REGISTER MAPS

The summaries of the registers associated with the dsPIC33F Input Capture module are provided in Table 12-3, Table 12-4 and Table 12-5.

#### Table 12-3: Input Capture Register Map

| File Name | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7         | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|--------|--------|--------|--------|--------|--------|-------|------------|---------------|-------|-------|-------|-------|-------|-------|-------|---------------|

| ICxBUF    |        |        |        |        |        |        |       | Input Capt | ture x Regist | er    |       |       |       |       |       |       | xxxx          |

| ICxCON    | _      | _      | ICSIDL | _      | _      | _      | _     | _          | ICTMR         | ICI1  | ICI0  | ICOV  | ICBNE | ICM2  | ICM1  | ICM0  | 0000          |

|           |        |        |        |        |        | (      |       |            |               |       |       |       |       |       |       |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### Table 12-4: Timer Register Map

|           |                 | ici itegis |        |             |        |        |       |          |            |       |        |        |       |       |       |       |               |

|-----------|-----------------|------------|--------|-------------|--------|--------|-------|----------|------------|-------|--------|--------|-------|-------|-------|-------|---------------|

| File Name | Bit 15          | Bit 14     | Bit 13 | Bit 12      | Bit 11 | Bit 10 | Bit 9 | Bit 8    | Bit 7      | Bit 6 | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR2      | Timer2 Register |            |        |             |        |        |       |          |            |       |        |        | xxxx  |       |       |       |               |

| TMR3      | Timer3 Register |            |        |             |        |        |       |          |            |       |        | xxxx   |       |       |       |       |               |

| PR2       |                 |            |        |             |        |        |       | Period I | Register 2 |       |        |        |       |       |       |       | FFFF          |

| PR3       |                 |            |        |             |        |        |       | Period I | Register 3 |       |        |        |       |       |       |       | FFFF          |

| T2CON     | TON             | _          | TSIDL  | _           | _      | _      | _     | _        | _          | TGATE | TCKPS1 | TCKPS0 | T32   | _     | TCS   | _     | 0000          |

| T3CON     | TON             |            | TSIDL  | —           | —      | _      |       | _        |            | TGATE | TCKPS1 | TCKPS0 | _     |       | TCS   | -     | 0000          |

| Lonondi   |                 |            | Deest  | unimenterne |        |        |       |          |            |       |        |        |       |       |       |       |               |

Legend: x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### Table 12-5: Interrupt Controller Register Map

| File Name | Bit 15 | Bit 14 | Bit 13     | Bit 12 | Bit 11 | Bit 10 | Bit 9      | Bit 8 | Bit 7 | Bit 6 | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1      | Bit 0 | All<br>Resets |

|-----------|--------|--------|------------|--------|--------|--------|------------|-------|-------|-------|------------|-------|-------|-------|------------|-------|---------------|

| IFS0      | _      | _      | —          | —      | —      | _      | —          | —     | —     | —     | IC2IF      | -     | —     | —     | IC1IF      | —     | 0000          |

| IFS1      | _      | _      | _          | _      | _      | _      | _          | _     | IC8IF | IC7IF | —          | -     | —     | _     | —          | —     | 0000          |

| IFS2      |        | _      | _          | _      | _      | _      | _          | IC6IF | IC5IF | IC4IF | IC3IF      | _     | _     | _     | _          | _     | 0000          |

| IEC0      |        | _      | _          | _      | _      | _      | _          | _     | _     | _     | IC2IE      | _     | _     | _     | IC1IE      | _     | 0000          |

| IEC1      |        | _      | _          | _      | _      | _      | _          | _     | IC8IE | IC7IE | _          | _     | _     | _     | _          | _     | 0000          |

| IEC2      |        | _      | _          | _      | _      | _      | _          | IC6IE | IC5IE | IC4IE | IC3IE      | _     | _     | _     | _          | _     | 0000          |

| IPC0      |        | _      | _          | _      | _      | _      | _          | _     | _     |       | IC1IP<2:0> |       | _     | _     | _          | _     | 4444          |

| IPC1      |        | _      | _          | _      | _      | _      | _          | _     | _     |       | IC2IP<2:0> |       | _     | _     | _          | _     | 4440          |

| IPC5      |        |        | IC8IP<2:0> |        | _      |        | IC7IP<2:0> |       | _     | _     | _          | _     | _     | _     | _          | _     | 4440          |

| IPC9      | _      |        | IC5IP<2:0> |        | _      |        | IC4IP<2:0> |       | _     |       | IC3IP<2:0> |       | _     | _     | _          | —     | 4440          |

| IPC10     | _      | _      | _          | _      | _      | _      | _          | _     | _     | _     | _          | _     | _     |       | IC6IP<2:0> |       | 4440          |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 12.9 DESIGN TIPS

- Question 1: Can the Input Capture module be used to wake the device from Sleep mode?

- Answer: Yes. When the Input Capture module is configured to ICM<2:0> = 111 and the respective Channel Interrupt Enable bit is set (ICxIE = 1), a rising edge on the capture pin wakes up the device from Sleep mode (refer to 12.6 "Input Capture Operation in Power-Saving Modes").

# 12.10 RELATED APPLICATION NOTES

This section lists application notes that are related to this section of the manual. These application notes may not be written specifically for the dsPIC33F device family, but the concepts are pertinent and could be used with modification and possible limitations. The current application notes related to the Input Capture module are:

| Title                           | Application Note # |

|---------------------------------|--------------------|

| Using the CCP Module(s)         | AN594              |

| Implementing Ultrasonic Ranging | AN597              |

**Note:** For additional application notes and code examples for the dsPIC33F family of devices, visit the Microchip web site (www.microchip.com).

# 12.11 REVISION HISTORY

## **Revision A (March 2007)**

This is the initial released version of this document.

## Revision B (April 2007)

Minor edits have been incorporated throughout the document.

## Revision C (July 2009)

This revision incorporates the following updates:

- Examples:

- Updated Example 12-1 as per the code example explanation.

- Sections:

- The sub-heading Revision B (April 2007), in **12.11 "Revision History"** has been corrected as Revision A (March 2007).

- Additional minor corrections such as language and formatting updates are incorporated throughout the document.

Input Capture

NOTES: