# **Section 33. Device Configuration (Part II)**

### HIGHLIGHTS

This section of the manual contains the following major topics:

| Introduction                    |                                                                                                                                                  |

|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Device Configuration Registers  |                                                                                                                                                  |

| Configuration Bit Descriptions  |                                                                                                                                                  |

| Device Identification Registers | 33-11                                                                                                                                            |

| Register Map                    |                                                                                                                                                  |

| Related Application Notes       |                                                                                                                                                  |

| Revision History                |                                                                                                                                                  |

|                                 | Device Configuration Registers<br>Configuration Bit Descriptions<br>Device Identification Registers<br>Register Map<br>Related Application Notes |

#### 33.1 Introduction

The device configuration registers allow each user to customize certain aspects of the device to fit the needs of the application. Device configuration registers are non-volatile locations in program memory that hold settings for the dsPIC<sup>®</sup> DSC device during power-down. The device configuration registers hold global setup information for the device, such as the oscillator source, Watchdog Timer mode, code protection settings and others.

The device configuration registers are mapped in program memory locations, starting at address 0xF80000, and are accessible during normal device operation. This region is also referred to as "configuration space".

The Configuration bits can be programmed (read as '0') or left unprogrammed (read as '1') to select various device configurations.

#### 33.2 Device Configuration Registers

Each device configuration register is a 24-bit register. However, only the lower 16 bits of each register hold configuration data. The seven device configuration registers are as follows:

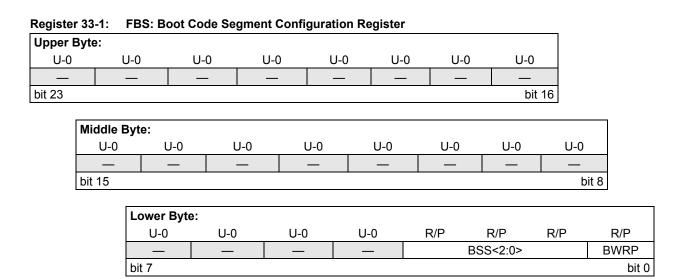

- FBS: Boot Code Segment Configuration Register

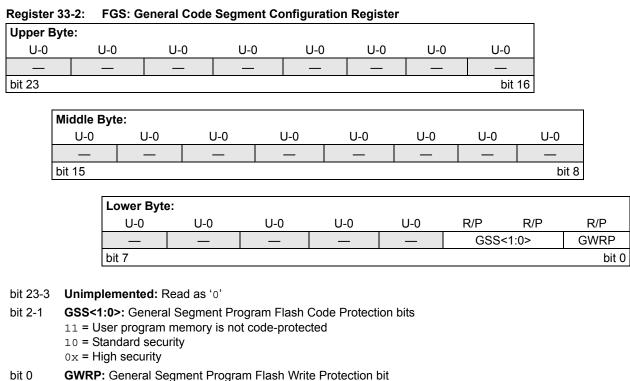

- FGS: General Code Segment Configuration Register

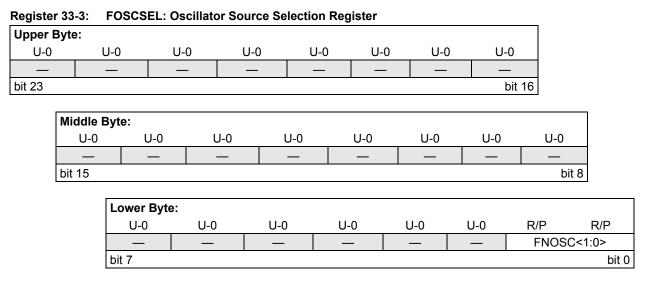

- FOSCSEL: Oscillator Source Selection Register

- FOSC: Oscillator Selection Configuration Register

- FWDT: Watchdog Timer Configuration Register

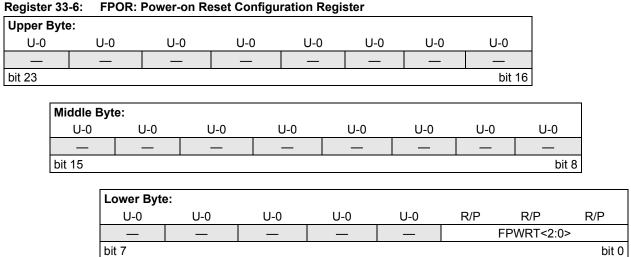

- FPOR: Power-on Reset Configuration Register

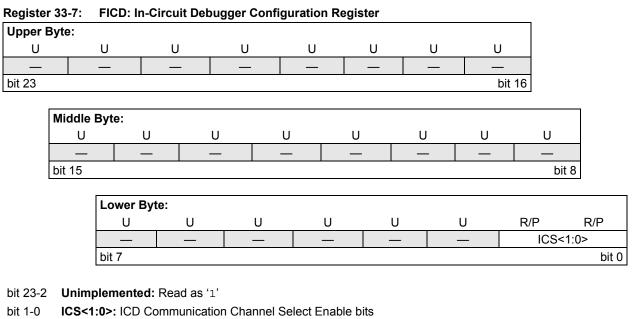

- FICD: In-Circuit Debugger Configuration Register

The device configuration registers can be programmed using Run-Time Self-Programming (RTSP), In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) or a device programmer.

**Note:** Some configuration registers and bits may not be present on all dsPIC30F devices. Refer the specific device data sheet for more information.

#### bit 23-4 Unimplemented: Read as '0'

- bit 3-1 **BSS<2:0>:** Boot Segment Program Flash Code Protection bits These bits select the boot segment program Flash code protection size and level (see the specific device data sheet for more information).

- bit 0 BWRP: Boot Segment Program Flash Write Protection bit

- 1 = Boot segment can be written

- 0 = Boot segment is write-protected

| Legend:          |                      |                       |  |

|------------------|----------------------|-----------------------|--|

| R = Readable bit | P = Programmable bit | U = Unimplemented bit |  |

33

## dsPIC30F Family Reference Manual

- **GWRP:** General Segment Program FI 1 = General segment can be written

- 0 = General segment is write-protected

| Legend:          |                      |                       |

|------------------|----------------------|-----------------------|

| R = Readable bit | P = Programmable bit | U = Unimplemented bit |

#### bit 23-2 Unimplemented: Read as '0'

- bit 1-0 FNOSC<1:0>: Initial Oscillator Source Selection bits

- 11 = Primary oscillator (HS, EC) with PLL module

- 10 = Primary oscillator (HS, EC)

- 01 = Internal Fast RC (FRC) oscillator with PLL module

- 00 = Internal Fast RC (FRC) oscillator

| Legend:          |                      |                       |

|------------------|----------------------|-----------------------|

| R = Readable bit | P = Programmable bit | U = Unimplemented bit |

## dsPIC30F Family Reference Manual

#### bit 23-8 Unimplemented: Read as '0'

bit 7

- bit 7-6 **FCKSM<1:0>:** Clock Switching and Monitor Selection Configuration bits

- 1x = Clock switching is disabled; fail-safe clock monitor is disabled

- 01 = Clock switching is enabled; fail-safe clock monitor is disabled

- 00 = Clock switching is enabled; fail-safe clock monitor is enabled

- bit 5 **FRANGE:** Frequency Range Select for FRC and PLL bit This bit acts like a "Gear Shift" feature that enables the dsPIC DSC device to operate at reduced MIPS at a reduced supply voltage (3.3V).

| FRANGE<br>Bit Value | Temperature<br>Rating | FRC Frequency<br>(Nominal) | PLL VCO<br>(Nominal)   |

|---------------------|-----------------------|----------------------------|------------------------|

| 1 = High Range      | Industrial            | 14.55 MHz                  | 466 MHz (480 MHz max.) |

|                     | Extended              | 9.7 MHz                    | 310 MHz (320 MHz max.) |

| 0 = Low Range       | Industrial            | 9.7 MHz                    | 310 MHz (320 MHz max.) |

|                     | Extended              | 6.4 MHz                    | 205 MHz (211 MHz max.) |

#### bit 4-3 Unimplemented: Read as '0'

bit 2

- OSCIOFNC: OSC2 Pin I/O Enable bit

- 1 = CLKO output signal is active on the OSCO pin

- 0 = CLKO output is disabled

- bit 1-0 **POSCMD<1:0>:** Primary Oscillator Mode bits

- 11 = Primary Oscillator is disabled

- 10 = HS oscillator mode is selected

- 01 = Reserved

- 00 = External clock mode is selected

#### Legend: R = Readable bit

P = Programmable bit

U = Unimplemented bit

bit 0

| pper E               | Byte:                                                                                                                                                       |                                                                                                                                                                     |                                                                                  |                                                                                                       |                                                                                  |                                                                             |                                             |                              |     |     |                      |          |        |     |       |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------|------------------------------|-----|-----|----------------------|----------|--------|-----|-------|

| U-0                  | l                                                                                                                                                           | J-0                                                                                                                                                                 |                                                                                  | U-0                                                                                                   |                                                                                  | U-0                                                                         |                                             | U-0                          | U   | -0  | U-0                  | L        | J-0    |     |       |

|                      |                                                                                                                                                             |                                                                                                                                                                     |                                                                                  |                                                                                                       |                                                                                  |                                                                             |                                             |                              | _   | _   |                      | -        |        |     |       |

| it 23                |                                                                                                                                                             |                                                                                                                                                                     |                                                                                  |                                                                                                       |                                                                                  |                                                                             |                                             |                              |     |     |                      |          | bit 16 | 6   |       |

| i                    |                                                                                                                                                             |                                                                                                                                                                     |                                                                                  |                                                                                                       |                                                                                  |                                                                             |                                             |                              |     |     |                      |          |        |     |       |

|                      | Middle E<br>U-0                                                                                                                                             | -                                                                                                                                                                   | J-0                                                                              |                                                                                                       | U-0                                                                              |                                                                             | U-0                                         |                              | U-0 |     | U-0                  | U-0      |        | U-0 |       |

|                      | -0                                                                                                                                                          |                                                                                                                                                                     | <u> </u>                                                                         |                                                                                                       |                                                                                  |                                                                             |                                             |                              |     |     |                      | <u> </u> |        |     |       |

|                      | bit 15                                                                                                                                                      |                                                                                                                                                                     |                                                                                  |                                                                                                       |                                                                                  |                                                                             |                                             |                              |     |     |                      |          |        | b   | oit 8 |

|                      |                                                                                                                                                             |                                                                                                                                                                     |                                                                                  |                                                                                                       |                                                                                  |                                                                             |                                             |                              |     |     |                      |          |        |     |       |

|                      |                                                                                                                                                             | Lower                                                                                                                                                               | Byte                                                                             | :                                                                                                     |                                                                                  |                                                                             |                                             |                              |     |     |                      |          |        |     |       |

|                      | -                                                                                                                                                           | R/P                                                                                                                                                                 |                                                                                  | R/P                                                                                                   |                                                                                  | U-0                                                                         |                                             | R/P                          |     | R/P |                      | R/P      |        | R/P | R/P   |

|                      | -                                                                                                                                                           | FWDTE                                                                                                                                                               | ĪN                                                                               | WIND                                                                                                  | S                                                                                |                                                                             |                                             | WDTPF                        | RE  |     | 1                    | WDTPO    | ST<3   | :0> |       |

|                      |                                                                                                                                                             | bit 7                                                                                                                                                               |                                                                                  |                                                                                                       |                                                                                  |                                                                             |                                             |                              |     |     |                      |          |        |     | b     |

|                      | 1 = Wa<br>the<br>0 = Wa<br>SW                                                                                                                               | tchdog<br>RCON<br>tchdog<br>/DTEN I                                                                                                                                 | Time<br>regis<br>Time<br>pit in                                                  | ster will<br>r is ena<br>the RC                                                                       | ays en<br>have r<br>bled/d<br>ON re                                              | abled<br>no effe<br>isable<br>gister)                                       | (LPR)<br>ct.)<br>d by tl                    | C oscilla<br>he user a       |     |     | e disable<br>LPRC ca |          |        |     |       |

| it 7<br>it 6         | 1 = Wa<br>the<br>0 = Wa<br>SW<br>WINDI<br>1 = Wa                                                                                                            | tchdog<br>RCON<br>tchdog<br>/DTEN I<br>S: Watcl<br>tchdog                                                                                                           | Time<br>regis<br>Time<br>oit in<br>hdog<br>Time                                  | r is alwa<br>ster will<br>r is ena<br>the RC<br>Timer \<br>r in Nor                                   | ays en<br>have r<br>bled/d<br>ON re<br>Windo<br>n-wind                           | abled<br>no effe<br>isable<br>gister)<br>w Disa<br>ow mo                    | (LPR(<br>ect.)<br>d by th<br>able bi        | C oscilla<br>he user a       |     |     |                      |          |        |     |       |

| it 6                 | 1 = Wa<br>the<br>0 = Wa<br>SW<br>WINDI<br>1 = Wa<br>0 = Wa                                                                                                  | tchdog<br>RCON<br>tchdog<br>/DTEN t<br>5: Watcl<br>tchdog<br>tchdog                                                                                                 | Time<br>regis<br>Time<br>oit in<br>hdog<br>Time<br>Time                          | r is alwa<br>ster will<br>r is ena<br>the RC<br>Timer V<br>r in Nor<br>r in Win                       | ays en<br>have r<br>bled/d<br>ON re<br>Windo<br>n-wind                           | abled<br>no effe<br>isable<br>gister)<br>w Disa<br>ow mo                    | (LPR(<br>ect.)<br>d by th<br>able bi        | C oscilla<br>he user a       |     |     |                      |          |        |     |       |

| it 6<br>it 5         | 1 = Wa<br>the<br>0 = Wa<br>SW<br>WINDI<br>1 = Wa<br>0 = Wa                                                                                                  | tchdog<br>RCON<br>tchdog<br>/DTEN I<br>S: Watcl<br>tchdog<br>tchdog                                                                                                 | Time<br>regis<br>Time<br>oit in<br>hdog<br>Time<br>Time<br><b>ed:</b> R          | r is alwa<br>ster will<br>r is ena<br>the RC<br>Timer \<br>Timer \<br>r in Nor<br>r in Win<br>Read as | ays en<br>have r<br>bled/d<br>ON re<br>Windo<br>n-wind<br>idow n<br>'o'          | abled<br>no effe<br>isable<br>gister)<br>w Disa<br>ow mo<br>node            | (LPR(<br>ct.)<br>d by th<br>able bi<br>ode  | C oscilla<br>he user a       |     |     |                      |          |        |     |       |

| t 6<br>t 5           | 1 = Wa<br>the<br>0 = Wa<br>SW<br>WINDIA<br>1 = Wa<br>0 = Wa<br>Unimp<br>WDTP<br>1 = 1:1                                                                     | tchdog<br>RCON<br>tchdog<br>/DTEN t<br>S: Watcl<br>tchdog<br>tchdog<br>lemente<br>RE: Wat<br>28                                                                     | Time<br>regis<br>Time<br>oit in<br>hdog<br>Time<br>Time<br><b>ed:</b> R          | r is alwa<br>ster will<br>r is ena<br>the RC<br>Timer \<br>Timer \<br>r in Nor<br>r in Win<br>Read as | ays en<br>have r<br>bled/d<br>ON re<br>Windo<br>n-wind<br>idow n<br>'o'          | abled<br>no effe<br>isable<br>gister)<br>w Disa<br>ow mo<br>node            | (LPR(<br>ct.)<br>d by th<br>able bi<br>ode  | C oscilla<br>he user a       |     |     |                      |          |        |     |       |

| it 6<br>it 5<br>it 4 | 1 = Wa<br>the<br>0 = Wa<br>SW<br><b>WINDI</b><br>1 = Wa<br>0 = Wa<br><b>Unimp</b><br><b>WDTPI</b><br>1 = 1:1<br>0 = 1:3                                     | tchdog<br>RCON<br>tchdog<br>/DTEN I<br>S: Watcl<br>tchdog<br>tchdog<br>Iemente<br>RE: Wat<br>28<br>2                                                                | Time<br>regis<br>Time<br>bit in<br>hdog<br>Time<br>Time<br><b>ed:</b> R          | r is alwaster will<br>r is ena<br>the RC<br>Timer V<br>r in Nor<br>r in Win<br>Read as<br>og Time     | ays en<br>have r<br>bled/d<br>ON re<br>Windo<br>h-wind<br>dow n<br>'0'<br>r Pres | abled<br>no effe<br>isable<br>gister)<br>w Disa<br>ow mo<br>node<br>caler b | (LPR)<br>cct.)<br>d by th<br>able bi<br>ode | C oscilla<br>he user a<br>it |     |     |                      |          |        |     |       |

| t 6<br>t 5<br>t 4    | 1 = Wa<br>the<br>0 = Wa<br>SW<br>WINDI:<br>1 = Wa<br>0 = Wa<br>Unimp<br>WDTPI<br>1 = 1:1<br>0 = 1:3<br>WDTPI<br>1111 =                                      | tchdog<br>RCON<br>tchdog<br>/DTEN I<br>S: Watcl<br>tchdog<br>tchdog<br>lemente<br>RE: Wat<br>28<br>2<br>DST<3:<br>1:32,76                                           | Time<br>regis<br>Time<br>bit in<br>hdog<br>Time<br>Time<br><b>ed:</b> R<br>tchdc | r is alwaster will<br>r is ena<br>the RC<br>Timer V<br>r in Nor<br>r in Win<br>Read as<br>og Time     | ays en<br>have r<br>bled/d<br>ON re<br>Windo<br>h-wind<br>dow n<br>'0'<br>r Pres | abled<br>no effe<br>isable<br>gister)<br>w Disa<br>ow mo<br>node<br>caler b | (LPR)<br>cct.)<br>d by th<br>able bi<br>ode | C oscilla<br>he user a<br>it |     |     |                      |          |        |     |       |

| t 6<br>t 5<br>t 4    | 1 = Wa<br>the<br>0 = Wa<br>SW<br>WINDI:<br>1 = Wa<br>0 = Wa<br>Unimp<br>WDTPI<br>1 = 1:1<br>0 = 1:3<br>WDTPI<br>1111 =                                      | tchdog<br>RCON<br>tchdog<br>/DTEN I<br>S: Watcl<br>tchdog<br>tchdog<br>Iemente<br>RE: Wat<br>28<br>2<br>DST<3:                                                      | Time<br>regis<br>Time<br>bit in<br>hdog<br>Time<br>Time<br><b>ed:</b> R<br>tchdc | r is alwaster will<br>r is ena<br>the RC<br>Timer V<br>r in Nor<br>r in Win<br>Read as<br>og Time     | ays en<br>have r<br>bled/d<br>ON re<br>Windo<br>h-wind<br>dow n<br>'0'<br>r Pres | abled<br>no effe<br>isable<br>gister)<br>w Disa<br>ow mo<br>node<br>caler b | (LPR)<br>cct.)<br>d by th<br>able bi<br>ode | C oscilla<br>he user a<br>it |     |     |                      |          |        |     |       |

| t 6<br>t 5<br>t 4    | 1 = Wa<br>the<br>0 = Wa<br>SW<br>WINDI:<br>1 = Wa<br>0 = Wa<br>Unimp<br>WDTPI<br>1 = 1:1<br>0 = 1:3<br>WDTPI<br>1111 =                                      | tchdog<br>RCON<br>tchdog<br>/DTEN I<br>S: Watcl<br>tchdog<br>tchdog<br>lemente<br>RE: Wat<br>28<br>2<br>DST<3:<br>1:32,76                                           | Time<br>regis<br>Time<br>bit in<br>hdog<br>Time<br>Time<br><b>ed:</b> R<br>tchdc | r is alwaster will<br>r is ena<br>the RC<br>Timer V<br>r in Nor<br>r in Win<br>Read as<br>og Time     | ays en<br>have r<br>bled/d<br>ON re<br>Windo<br>h-wind<br>dow n<br>'0'<br>r Pres | abled<br>no effe<br>isable<br>gister)<br>w Disa<br>ow mo<br>node<br>caler b | (LPR)<br>cct.)<br>d by th<br>able bi<br>ode | C oscilla<br>he user a<br>it |     |     |                      |          |        |     |       |

| t 6<br>t 5           | 1 = Wa<br>the<br>0 = Wa<br>SW<br><b>WINDI</b><br>1 = Wa<br>0 = Wa<br><b>Unimp</b><br><b>WDTPI</b><br>1 = 1:1<br>0 = 1:3<br><b>WDTPI</b><br>1111 =<br>1110 = | tchdog<br>RCON<br>tchdog<br>/DTEN I<br><b>S:</b> Watcl<br>tchdog<br>tchdog<br><b>lemente</b><br><b>RE:</b> Wat<br>28<br>2<br><b>DST&lt;3:</b><br>1:32,76<br>1:15,38 | Time<br>regis<br>Time<br>bit in<br>hdog<br>Time<br>Time<br><b>ed:</b> R<br>tchdc | r is alwaster will<br>r is ena<br>the RC<br>Timer V<br>r in Nor<br>r in Win<br>Read as<br>og Time     | ays en<br>have r<br>bled/d<br>ON re<br>Windo<br>h-wind<br>dow n<br>'0'<br>r Pres | abled<br>no effe<br>isable<br>gister)<br>w Disa<br>ow mo<br>node<br>caler b | (LPR)<br>cct.)<br>d by th<br>able bi<br>ode | C oscilla<br>he user a<br>it |     |     |                      |          |        |     |       |

| t 6<br>t 5<br>t 4    | 1 = Wa<br>the<br>0 = Wa<br>SW<br>WINDI:<br>1 = Wa<br>0 = Wa<br>Unimp<br>WDTPI<br>1 = 1:1<br>0 = 1:3<br>WDTPI<br>1111 =<br>1110 =                            | tchdog<br>RCON<br>tchdog<br>/DTEN I<br>S: Watcl<br>tchdog<br>tchdog<br>Iemente<br>RE: Wat<br>28<br>2<br>DST<3:<br>1:32,76<br>1:15,38                                | Time<br>regis<br>Time<br>bit in<br>hdog<br>Time<br>Time<br><b>ed:</b> R<br>tchdc | r is alwaster will<br>r is ena<br>the RC<br>Timer V<br>r in Nor<br>r in Win<br>Read as<br>og Time     | ays en<br>have r<br>bled/d<br>ON re<br>Windo<br>h-wind<br>dow n<br>'0'<br>r Pres | abled<br>no effe<br>isable<br>gister)<br>w Disa<br>ow mo<br>node<br>caler b | (LPR)<br>cct.)<br>d by th<br>able bi<br>ode | C oscilla<br>he user a<br>it |     |     |                      |          |        |     |       |

| t 6<br>t 5<br>t 4    | 1 = Wa<br>the<br>0 = Wa<br>SW<br><b>WINDI</b><br>1 = Wa<br>0 = Wa<br><b>Unimp</b><br><b>WDTPI</b><br>1 = 1:1<br>0 = 1:3<br><b>WDTPI</b><br>1111 =<br>1110 = | tchdog<br>RCON<br>tchdog<br>/DTEN I<br>S: Watcl<br>tchdog<br>tchdog<br>Iemente<br>RE: Wat<br>28<br>2<br>DST<3:<br>1:32,76<br>1:15,38                                | Time<br>regis<br>Time<br>bit in<br>hdog<br>Time<br>Time<br><b>ed:</b> R<br>tchdc | r is alwaster will<br>r is ena<br>the RC<br>Timer V<br>r in Nor<br>r in Win<br>Read as<br>og Time     | ays en<br>have r<br>bled/d<br>ON re<br>Windo<br>h-wind<br>dow n<br>'0'<br>r Pres | abled<br>no effe<br>isable<br>gister)<br>w Disa<br>ow mo<br>node<br>caler b | (LPR)<br>cct.)<br>d by th<br>able bi<br>ode | C oscilla<br>he user a<br>it |     |     |                      |          |        |     |       |

| t 6<br>t 5<br>t 4    | 1 = Wa<br>the<br>0 = Wa<br>SW<br>WINDI:<br>1 = Wa<br>0 = Wa<br>Unimp<br>WDTPI<br>1 = 1:1<br>0 = 1:3<br>WDTPI<br>1111 =<br>1110 =                            | tchdog<br>RCON<br>tchdog<br>/DTEN I<br>S: Watcl<br>tchdog<br>tchdog<br>Iemente<br>RE: Wat<br>28<br>2<br>OST<3:<br>1:32,76<br>1:15,38<br>1:2<br>1:11                 | Time<br>regis<br>Time<br>bit in<br>hdog<br>Time<br>Time<br><b>ed:</b> R<br>tchdc | r is alwaster will<br>r is ena<br>the RC<br>Timer V<br>r in Nor<br>r in Win<br>Read as<br>og Time     | ays en<br>have r<br>bled/d<br>ON re<br>Windo<br>h-wind<br>dow n<br>'0'<br>r Pres | abled<br>no effe<br>isable<br>gister)<br>w Disa<br>ow mo<br>node<br>caler b | (LPR)<br>cct.)<br>d by th<br>able bi<br>ode | C oscilla<br>he user a<br>it |     |     |                      |          |        |     |       |

## dsPIC30F Family Reference Manual

#### Register 33-6: FPOR: Power-on Reset Configuration Register

#### bit 23-3 Unimplemented: Read as '0'

bit 2-0 FPWRT<2:0>: Power-on Reset Timer Value Select bits (see the specific device data sheet for variations across temperature and voltage)

111 = PWRT = 128 ms 110 = PWRT = 64 ms 101 = PWRT = 32 ms 100 = PWRT = 16 ms 011 = PWRT = 8 ms 010 = PWRT = 4 ms 001 = PWRT = 2 ms 000 = PWRT = Disabled

| Legend:          |                      |                       |  |

|------------------|----------------------|-----------------------|--|

| R = Readable bit | P = Programmable bit | U = Unimplemented bit |  |

- 11 = Communicate on PGC1/EMUC1 and PGD1/EMUD1

- 10 = Communicate on PGC2/EMUC2 and PGD2/EMUD2

- 01 = Communicate on PGC3/EMUC3 and PGD3/EMUD3

- 00 = Reserved, do not use

| Legend:          |                      |                       |  |

|------------------|----------------------|-----------------------|--|

| R = Readable bit | P = Programmable bit | U = Unimplemented bit |  |

#### 33.3 Configuration Bit Descriptions

This section provides functional information for each of the device configuration bits.

#### 33.3.1 Code Protection and CodeGuard<sup>™</sup> Security

The dsPIC30F product family offers advanced security, which protects the Intellectual Property that users invest in collaborative system designs. CodeGuard<sup>™</sup> Security enables multiple parties to securely share resources (memory, interrupts and peripherals) on a single chip with assurance that their Intellectual Property rights are not at risk.

The code protection features are controlled by the Boot Code Segment (FBS) and General Code Segment (FGS) Configuration registers and vary from one dsPIC30F device to another. For further information, refer the specific device data sheet and refer to **Section 26**. **"CodeGuard™ Security"** (DS70275) in the "*dsPIC30F Family Reference Manual*".

#### 33.3.2 Oscillator Configuration Bits

The dsPIC30F clock selection, switching and configuration settings are controlled by the Oscillator Source Selection (FOSCSEL) and Oscillator Configuration (FOSC) registers. For more information, refer to **Section 29. "Oscillator"** (DS70268) in the "*dsPIC30F Family Reference Manual*".

#### 33.3.3 Power-on Reset Configuration Bits

The Power-on Reset (POR) Configuration bits in the Power-on Reset (FPOR) Configuration register are used to set the Power-up Timer delay time. For more information on these configuration bits, refer to **Section 8.** "**Reset**" (DS70055) in the "*dsPIC30F Family Reference Manual*".

#### 33.3.4 Watchdog Timer Configuration Bits

The dsPIC30F Watchdog Timer can be enabled and configured using the Watchdog Timer Configuration (FWDT) register. For more information on these configuration bits, refer to **Section 36. "Watchdog Timer and Power-Saving Modes (Part II)**" (DS70274) in the "dsPIC30F Family Reference Manual".

#### 33.4 Device Identification Registers

The dsPIC30F devices have two sets of Device ID registers located in configuration space that provide identification information.

#### 33.4.1 Device ID (DEVID) Registers

The configuration memory space locations 0xFF0000 and 0xFF0002 are used to store a read-only Device ID number that is set when the device is manufactured. This number identifies the dsPIC30F device type and the silicon revision.

The Device ID registers can be read using table read instructions.

#### 33.4.2 Unit ID Field

The Unit ID field is located at configuration memory space locations 0x8005C0 through 0x8005FE. This field consists of 32 program memory locations that can be programmed with unique device information using a device programmer. This field cannot be written or erased by the user application, but can be read using table read instructions.

Please contact Microchip technical support or your local Microchip representative for further details.

### 33.5 Register Map

A summary of the registers associated with dsPIC30F Device Configuration is provided in Table 33-1.

### Table 33-1: Device Configuration Register Map

| File Name | Bits 23-16 | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2      | Bit 1        | Bit 0   |

|-----------|------------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|-------|------------|--------------|---------|

| FBS       | —          | _      | _      | _      | _      | _      | —      | _     |       | —      | —      | _      | _      |       | BSS<2:0>   |              | BWRP    |

| FGS       | _          | -      | _      | _      | _      | _      | _      | _     | _     | _      | _      | _      | _      | _     | GSS<1      | :0>          | GWRP    |

| FOSCSEL   | _          | -      | _      | _      | _      | _      | _      | _     | _     | _      | _      | _      | _      | _     | _          | FNOS         | C<1:0>  |

| FOSC      | _          | -      | _      | _      | _      | _      | _      | _     | _     | FCKSN  | /<1:0> | FRANGE | _      | _     | OSCIOFNC   | POSCN        | 1D<1:0> |

| FWDT      | _          | -      | _      | _      | _      | _      | _      | _     | _     | FWDTEN | WINDIS | _      | WDTPRE |       | WDTPOS     | WDTPOST<3:0> |         |

| FPOR      | _          | _      | _      | _      | —      | —      | _      | —     |       | -      | _      | —      | _      | —     | FPWRT<2:0> |              |         |

| FICD      | —          | _      | _      | —      | _      | _      | _      | _     | -     | —      | _      | _      | —      | _     | —          | ICS<         | :1:0>   |

Note: Refer to the device data sheet for specific configuration register map details.

#### 33.6 Related Application Notes

This section lists application notes that are related to this section of the manual. These application notes may not be written specifically for the dsPIC30F product family, but the concepts are pertinent and could be used with modification and possible limitations. The current application notes related to Device Configuration include the following:

#### Title

#### Application Note #

No related application notes at this time.

**Note:** Please visit the Microchip web site (www.microchip.com) for additional Application Notes and code examples for the dsPIC30F family of devices.

33

#### 33.7 Revision History

#### **Revision A (February 2007)**

This is the initial release of this document.

### Revision B (January 2009)

- This revision includes the following corrections and updates:

- · Minor typographical and formatting corrections throughout the document

- Register Changes:

- Added FICD: In-Circuit Debugger Configuration Register (see Register 33-7)

- Table Changes:

- Added the FICD register map to the Device Configuration Register Map Table (see Table 33-1)