# HIGHLIGHTS

This section of the manual contains the following major topics:

| 21.1  | Introduction                                   | 21-2  |

|-------|------------------------------------------------|-------|

| 21.2  | Control Registers                              |       |

| 21.3  | UART Baud Rate Generator (BRG)                 | 21-9  |

| 21.4  | UART Configuration                             | 21-13 |

| 21.5  | UART Transmitter                               | 21-14 |

| 21.6  | UART Receiver                                  | 21-18 |

| 21.7  | Using the UART for 9-Bit Communication         | 21-21 |

| 21.8  | Receiving Break Characters                     | 21-23 |

| 21.9  | Initialization                                 | 21-23 |

| 21.10 | Other Features of the UART                     | 21-25 |

| 21.11 | UART Operation During CPU Sleep and Idle Modes | 21-27 |

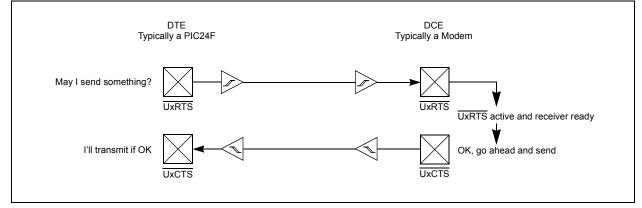

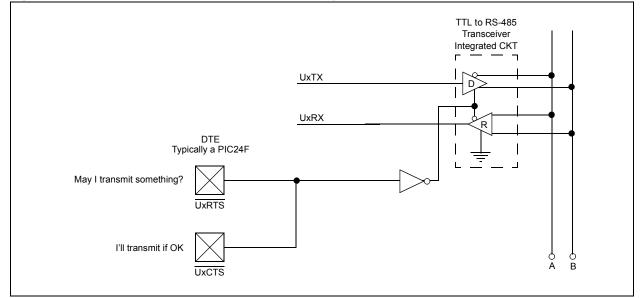

| 21.12 | Operation of UxCTS and UxRTS Control Pins      | 21-29 |

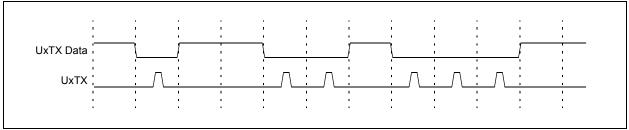

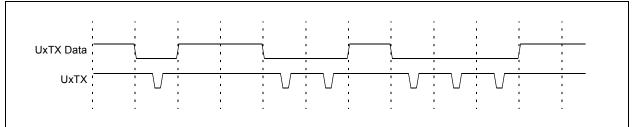

| 21.13 | Infrared Support                               | 21-31 |

| 21.14 | Registers Associated with the UART Module      | 21-34 |

| 21.15 | Electrical Specifications                      | 21-35 |

| 21.16 | Design Tips                                    | 21-36 |

| 21.17 | Related Application Notes                      | 21-37 |

| 21.18 | Revision History                               | 21-38 |

UART

# 21.1 INTRODUCTION

The Universal Asynchronous Receiver Transmitter (UART) module is one of the serial I/O modules available in the PIC24F device family. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers, using protocols such as RS-232, <u>RS-485</u>, LIN 1.2 and IrDA<sup>®</sup>. The module also supports the hardware flow control option with UxCTS and UxRTS pins and also includes the IrDA encoder and decoder.

The primary features of the UART module are:

- Full-Duplex, 8 or 9-Bit Data Transmission through the UxTX and UxRX pins

- Even, Odd or No Parity options (for 8-bit data)

- One or Two Stop bits

- Hardware Auto-Baud Feature

- Hardware Flow Control Option with UxCTS and UxRTS pins

- Fully Integrated Baud Rate Generator with 16-Bit Prescaler

- Baud Rates Ranging from 1 Mbps to 15 bps at 16 MIPS

- 4-Deep First-In-First-Out (FIFO) Transmit Data Buffer

- 4-Deep FIFO Receive Data Buffer

- Parity, Framing and Buffer Overrun Error Detection

- Support for 9-Bit Data mode with Address Detect (9th bit = 1)

- · Transmit and Receive Interrupts

- Loopback mode for Diagnostic Support

- IrDA Encoder and Decoder Logic

- LIN 1.2 Protocol Support

- 16x Baud Clock Output for External IrDA Encoder/Decoder Support

**Note:** Each PIC24F device variant may have one or more UART modules. An 'x' used in the names of pins, control/status bits and registers denotes the particular module. Refer to the specific device data sheets for more details.

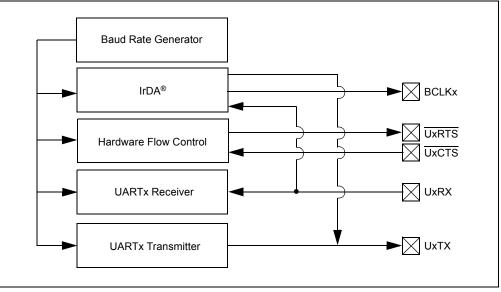

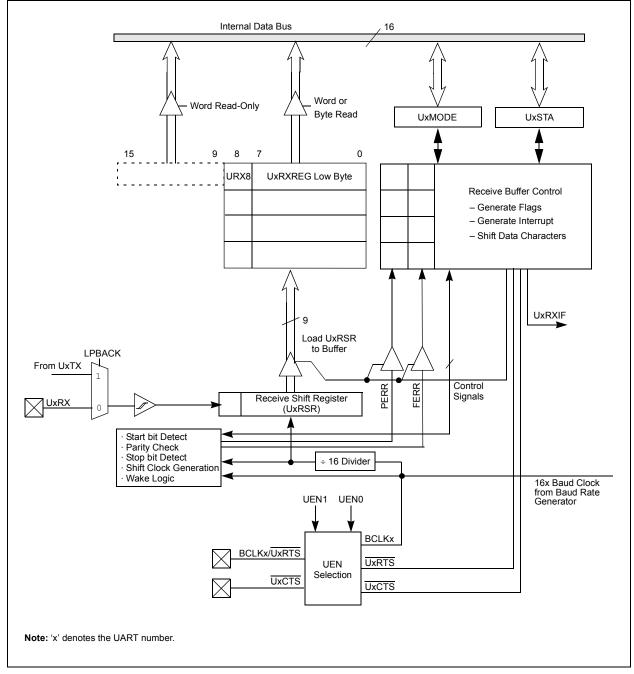

A simplified block diagram of the UARTx is shown in Figure 21-1. The UARTx module consists of the following key important hardware elements:

- · Baud Rate Generator

- Asynchronous Transmitter

- Asynchronous Receiver

#### Figure 21-1: UARTx Simplified Block Diagram

# 21.2 CONTROL REGISTERS

| Register 21-1:  | UXMODE: U                                                                                                                                                                            | JARIX Mode I      | kegister            |                  |                      |                  |              |  |  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|---------------------|------------------|----------------------|------------------|--------------|--|--|

| R/W-0           | R/W-0                                                                                                                                                                                | R/W-0             | R/W-0               | R/W-0            | R/W-0                | R/W-0            | R/W-0        |  |  |

| UARTEN          | UFRZ                                                                                                                                                                                 | USIDL             | IREN <sup>(1)</sup> | RTSMD            | ALTIO <sup>(2)</sup> | UEN1             | UEN0         |  |  |

| bit 15          |                                                                                                                                                                                      |                   |                     |                  |                      |                  | bit 8        |  |  |

| R/W-0           | R/W-0                                                                                                                                                                                | R/W-0             | R/W-0               | R/W-0            | R/W-0                | R/W-0            | R/W-0        |  |  |

| WAKE            | LPBACK                                                                                                                                                                               | ABAUD             | RXINV               | BRGH             | PDSEL1               | PDSEL0           | STSEL        |  |  |

| bit 7           |                                                                                                                                                                                      |                   |                     |                  |                      | bit              |              |  |  |

|                 |                                                                                                                                                                                      |                   |                     |                  |                      |                  |              |  |  |

| Legend:         |                                                                                                                                                                                      |                   |                     |                  |                      |                  |              |  |  |

| R = Readable    |                                                                                                                                                                                      | W = Writable      |                     | •                | mented bit, read     |                  |              |  |  |

| -n = Value at F | POR                                                                                                                                                                                  | '1' = Bit is set  |                     | '0' = Bit is cle | ared                 | x = Bit is unkr  | nown         |  |  |

| bit 15          | UARTEN: UA                                                                                                                                                                           | ARTx Enable bi    | t                   |                  |                      |                  |              |  |  |

|                 | 1 = UARTx is                                                                                                                                                                         | s enabled; UAI    | RTx pins are o      | controlled by U  | ARTx as define       | ed by UEN<1:0    | > and UTXEI  |  |  |

|                 | control b                                                                                                                                                                            |                   | - <b>-</b>          |                  |                      |                  |              |  |  |

| L:1 4 4         |                                                                                                                                                                                      |                   | -                   | controlled by co | prresponding Po      | ORT, LAT and T   | RIS DItS     |  |  |

| bit 14          |                                                                                                                                                                                      | e in Debug Mo     |                     | dulo fronzos o   | poration             |                  |              |  |  |

|                 | <ul> <li>1 = When emulator is in Debug mode, module freezes operation</li> <li>0 = When emulator is in Debug mode, module continues operation</li> </ul>                             |                   |                     |                  |                      |                  |              |  |  |

| bit 13          | USIDL: Stop in Idle Mode bit                                                                                                                                                         |                   |                     |                  |                      |                  |              |  |  |

|                 | 1 = Discontinue operation when device enters Idle mode                                                                                                                               |                   |                     |                  |                      |                  |              |  |  |

|                 | 0 = Continue operation in Idle mode                                                                                                                                                  |                   |                     |                  |                      |                  |              |  |  |

| bit 12          | IREN: IrDA Encoder and Decoder Enable bit <sup>(1)</sup>                                                                                                                             |                   |                     |                  |                      |                  |              |  |  |

|                 | 1 = IrDA encoder and decoder enabled<br>0 = IrDA encoder and decoder disabled                                                                                                        |                   |                     |                  |                      |                  |              |  |  |

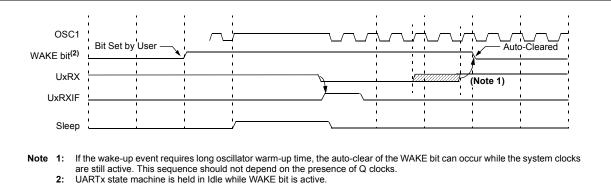

| bit 11          | <b>RTSMD:</b> Mode Selection for $\overline{\text{UxRTS}}$ Pin bit                                                                                                                   |                   |                     |                  |                      |                  |              |  |  |

|                 | 1 = UxRTS in Simplex mode                                                                                                                                                            |                   |                     |                  |                      |                  |              |  |  |

|                 | 0 = UxRTS in Flow Control mode                                                                                                                                                       |                   |                     |                  |                      |                  |              |  |  |

| bit 10          | ALTIO: UAR                                                                                                                                                                           | Tx Alternate I/C  | Selection bit       | (2)              |                      |                  |              |  |  |

|                 |                                                                                                                                                                                      | ommunicates u     |                     |                  |                      |                  |              |  |  |

|                 |                                                                                                                                                                                      | ommunicates u     | -                   | a uxkx I/O pii   | าร                   |                  |              |  |  |

| bit 9-8         |                                                                                                                                                                                      | IARTx Enable I    |                     | nabled and us    |                      | in controlled by | nort latabas |  |  |

|                 | <ul> <li>11 = UxTX, UxRX and BCLKx pins are enabled and used; UxCTS pin is controlled by port latches</li> <li>10 = UxTX, UxRX, UxCTS and UxRTS pins are enabled and used</li> </ul> |                   |                     |                  |                      |                  |              |  |  |

|                 | 01 = 0.000 (0.000 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                    |                   |                     |                  |                      |                  |              |  |  |

|                 | 00 = UxTX and UxRX pins are enabled and used; UxCTS, UxRTS and BCLKx pins are controlled by                                                                                          |                   |                     |                  |                      |                  |              |  |  |

| =               | port latches                                                                                                                                                                         |                   |                     |                  |                      |                  |              |  |  |

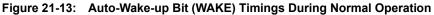

| bit 7           | WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit                                                                                                                       |                   |                     |                  |                      |                  |              |  |  |

|                 | 1 = Wake-up<br>0 = Wake-up                                                                                                                                                           |                   |                     |                  |                      |                  |              |  |  |

| bit 6           | •                                                                                                                                                                                    | ARTx Loopback     | Mode Select         | bit              |                      |                  |              |  |  |

|                 | 1 = Enable Loopback mode                                                                                                                                                             |                   |                     |                  |                      |                  |              |  |  |

|                 |                                                                                                                                                                                      | mode is disab     | led                 |                  |                      |                  |              |  |  |

| Note 1: This    | feature is availa                                                                                                                                                                    | able only for the | e 16x BRG mo        | ode (BRGH = '    | 0').                 |                  |              |  |  |

|                 |                                                                                                                                                                                      |                   |                     |                  |                      | ice data sheets  | for details. |  |  |

#### Register 21-1: UxMODE: UARTx Mode Register

UART

#### Register 21-1: UxMODE: UARTx Mode Register (Continued)

| bit 5   | ABAUD: Auto-Baud Enable bit                                                                                                                                                                                         |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>1 = Enable baud rate measurement on the next character. Requires reception of a Sync field (55h); cleared in hardware upon completion.</li> <li>0 = Baud rate measurement disabled or completed</li> </ul> |

| bit 4   | RXINV: Receive Polarity Inversion bit                                                                                                                                                                               |

|         | 1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                                                            |

| bit 3   | BRGH: High Baud Rate Select bit                                                                                                                                                                                     |

|         | 1 = High speed<br>0 = Low speed                                                                                                                                                                                     |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                                                          |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                                                       |

| bit 0   | STSEL: Stop Selection bit                                                                                                                                                                                           |

|         | 1 = 2 Stop bits<br>0 = 1 Stop bit                                                                                                                                                                                   |

- Note 1: This feature is available only for the 16x BRG mode (BRGH = '0').

2: The alternate UART I/O pins are not available on all devices. See specific device data sheets for details.

| Register 21-2:      | : UxSTA: UA                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | RTx Status an                                                                                                                                          | d Control Re                                                                                                 | egister                                                                     |                                                                    |                                                          |                 |

|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------|----------------------------------------------------------|-----------------|

| R/W-0               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                  | U-0                                                                                                          | R/W-0                                                                       | R/W-0                                                              | R-0                                                      | R-1             |

| UTXISEL1            | UTXINV                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | UTXISEL0                                                                                                                                               |                                                                                                              | UTXBRK                                                                      | UTXEN                                                              | UTXBF                                                    | TRMT            |

| bit 15              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                        |                                                                                                              |                                                                             |                                                                    |                                                          | bit 8           |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                        |                                                                                                              |                                                                             |                                                                    |                                                          |                 |

| R/W-0               | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                  | R-1                                                                                                          | R-0                                                                         | R-0                                                                | R/C-0                                                    | R-0             |

| URXISEL1            | URXISEL0                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ADDEN                                                                                                                                                  | RIDLE                                                                                                        | PERR                                                                        | FERR                                                               | OERR                                                     | URXDA           |

| bit 7               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                        |                                                                                                              |                                                                             |                                                                    |                                                          | bit 0           |

| Legend:             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | C = Clearable                                                                                                                                          | bit                                                                                                          |                                                                             |                                                                    |                                                          |                 |

| R = Readable        | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | W = Writable I                                                                                                                                         |                                                                                                              | U = Unimpler                                                                | nented bit, rea                                                    | d as '0'                                                 |                 |

| -n = Value at I     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | '1' = Bit is set                                                                                                                                       |                                                                                                              | '0' = Bit is cle                                                            |                                                                    | x = Bit is unki                                          | nown            |

| bit 15,13<br>bit 14 | <ul> <li>11 = Reserve</li> <li>10 = Interrup<br/>transmit</li> <li>01 = Interrup<br/>Shift Re</li> <li>00 = Interrup<br/>at least</li> <li>UTXINV: Trar</li> <li>IREN = 0:</li> <li>1 = UxTX Idle</li> <li>IREN = 1:</li> <li>1 = IrDA ence</li> </ul>                                                                                                                                                                                                                        | t generated wit<br>t buffer become<br>t generated wh<br>egister) and all t<br>t generated wh<br>one location is<br>nsmit Polarity In<br>e state is '0' | hen a charac<br>es empty<br>en the last tra<br>he transmit o<br>en any chara<br>empty in the<br>iversion bit | cter is transfer<br>ansmission is o<br>perations are c<br>cter is transferr | red to the Tra<br>ver (last charac<br>completed<br>ed to the Trans | nsmit Shift Re<br>cter shifted out o<br>mit Shift Regist | of the Transmit |

| bit 12              | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ted: Read as '                                                                                                                                         | )'                                                                                                           |                                                                             |                                                                    |                                                          |                 |

| bit 11              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | ansmit Break bi                                                                                                                                        |                                                                                                              |                                                                             |                                                                    |                                                          |                 |

| bit 10              | <ol> <li>UxTX pin is driven low regardless of transmitter state (Sync Break transmission – Start bit followed by twelve '0's and followed by a Stop bit)</li> <li>Sync Break transmission is disabled or completed</li> <li>UTXEN: Transmit Enable bit</li> <li>UARTx transmitter enabled, UxTX pin controlled by UARTx (if UARTEN = 1)</li> <li>UARTx transmitter disabled, any pending transmission is aborted and buffer is reset. UxTX pin controlled by PORT.</li> </ol> |                                                                                                                                                        |                                                                                                              |                                                                             |                                                                    |                                                          |                 |

| bit 9               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | smit Buffer Full                                                                                                                                       | Status bit (re                                                                                               | ad-only)                                                                    |                                                                    |                                                          |                 |

|                     | 1 = Transmit I                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                        |                                                                                                              |                                                                             | d can be writte                                                    | n                                                        |                 |

| bit 8               | TRMT: Transr                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | mit Shift Registe                                                                                                                                      | er is Empty b                                                                                                | it (read-only)                                                              |                                                                    |                                                          |                 |

|                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                        |                                                                                                              |                                                                             |                                                                    | t transmission h<br>r queued in the                      |                 |

| bit 7-6             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 0>: Receive Int                                                                                                                                        | -                                                                                                            |                                                                             |                                                                    |                                                          |                 |

|                     | 10 = Interrupt<br>0x = Interrupt                                                                                                                                                                                                                                                                                                                                                                                                                                              | t flag bit is set w<br>t flag bit is set w<br>t flag bit is set w                                                                                      | /hen receive<br>/hen a charao                                                                                | buffer is 3/4 ful<br>cter is received                                       | l (i.e., has 3 da                                                  | ,                                                        |                 |

| bit 5               | 1 = Address [                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ress Character<br>Detect mode en<br>Detect mode dis                                                                                                    | abled. If 9-bi                                                                                               |                                                                             |                                                                    | ntrol bit has no                                         | effect.         |

21

...

. .

## Register 21-2: UxSTA: UARTx Status and Control Register (Continued)

| bit 4 | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Data is being received                                                                                                          |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                                           |

|       | <ul> <li>1 = Parity error has been detected for the current character</li> <li>0 = Parity error has not been detected</li> </ul>                                                                    |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                                          |

|       | <ul> <li>1 = Framing error has been detected for the current character</li> <li>0 = Framing error has not been detected</li> </ul>                                                                  |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (clear/read-only)                                                                                                                                     |

|       | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed (clearing a previously set OERR bit will reset the receiver buffer<br/>and RSR to empty state)</li> </ul> |

| bit 0 | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                                                |

|       | 1 = Receive buffer has data, at least one more character can be read                                                                                                                                |

0 = Receive buffer is empty

# Section 21. UART

| Register 21-3: | UxRXREG: | UARTx Receiv | ve Register |       |     |     |

|----------------|----------|--------------|-------------|-------|-----|-----|

| U-0            | U-0      | U-0          | U-0         | U-0   | U-0 | U-0 |

| _              | —        | —            | —           | —     | —   | —   |

| bit 15         |          |              |             |       |     |     |

|                |          |              |             |       |     |     |

| R-0            | R-0      | R-0          | R-0         | R-0   | R-0 | R-0 |

|                |          |              | URX         | <7:0> |     |     |

bit 0

bit 8

R-0

URX8

R-0

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-9 | Unimplemented: Read as '0'                                 |

|----------|------------------------------------------------------------|

| bit 8    | URX8: Data bit 8 of the Received Character (in 9-bit mode) |

| bit 7-0  | URX<7:0>: Data bits 7-0 of the Received Character          |

# Register 21-4: UxTXREG: UARTx Transmit Register (Write-Only)

bit 7

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | W-x   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   | —   | _   | _   | —   | —   | UTX8  |

| bit 15 |     |     |     |     |     |     | bit 8 |

| W-x   | W-x | W-x | W-x | W-x   | W-x | W-x | W-x   |

|-------|-----|-----|-----|-------|-----|-----|-------|

|       |     |     | UTX | <7:0> |     |     |       |

| bit 7 |     |     |     |       |     |     | bit 0 |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

| bit 15-9 | Unimplemented: Read as '0'                                    |

|----------|---------------------------------------------------------------|

| bit 8    | UTX8: Data bit 8 of the Transmitted Character (in 9-bit mode) |

| bit 7-0  | URX<7:0>: Data bits 7-0 of the Transmitted Character          |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | W-x   |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | BRG   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | BRO   | G<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | oit   | U = Unimpler     | mented bit, rea | d as '0'        |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

# Register 21-5: UxBRG: UARTx Baud Rate Generator Register

bit 15-0 BRG<15:0>: Baud Rate Generator Divisor bits

# 21.3 UART BAUD RATE GENERATOR (BRG)

The UART module includes a dedicated 16-bit Baud Rate Generator. The UxBRG register controls the period of a free-running, 16-bit timer. Equation 21-1 shows the formula for computation of the baud rate with BRGH = 0.

Equation 21-1: UART Baud Rate with BRGH = 0

Baud Rate =

$$\frac{FCY}{16 \cdot (UxBRG + 1)}$$

$$UxBRG = \frac{FCY}{16 \cdot Baud Rate} - 1$$

**Note:** FCY denotes the instruction cycle clock frequency (FOSC/2).

Example 21-1 shows the calculation of the baud rate error for the following conditions:

- Fcy = 4 MHz

- Desired Baud Rate = 9600

| Example 21-1: | Baud Rate Error Calculation (BRGH = 0) | ) |

|---------------|----------------------------------------|---|

|---------------|----------------------------------------|---|

| Desired Baud Rate       | =           | FCY/(16 (UxBRG + 1))                                                                           |

|-------------------------|-------------|------------------------------------------------------------------------------------------------|

| Solving for UxBRG val   | lue:        |                                                                                                |

| UxBRG<br>UxBRG<br>UxBRG | =<br>=<br>= | ( (FCY/Desired Baud Rate)/16) – 1<br>((4000000/9600)/16) – 1<br>25                             |

| Calculated Baud Rate    | =           | 4000000/(16 (25 + 1))<br>9615                                                                  |

| Error                   | =           | (Calculated Baud Rate – Desired Baud Rate)<br>Desired Baud Rate<br>(9615 – 9600)/9600<br>0.16% |

The maximum baud rate (BRGH = 0) possible is Fcy/16 (for UxBRG = 0), and the minimum baud rate possible is Fcy/16 \* 65536.

Equation 21-2 shows the formula for computation of the baud rate with BRGH = 1.

Equation 21-2: UART Baud Rate with BRGH = 1

Baud Rate =

$$\frac{FCY}{4 \cdot (UxBRG + 1)}$$

UxBRG =  $\frac{FCY}{4 \cdot Baud Rate} - 1$

**Note:** FCY denotes the instruction cycle clock frequency.

The maximum baud rate (BRGH = 1) possible is Fcy/4 (for UxBRG = 0), and the minimum baud rate possible is Fcy/(4 \* 65536).

Writing a new value to the UxBRG register causes the BRG timer to be reset (cleared). This ensures the BRG does not wait for a timer overflow before generating the new baud rate.

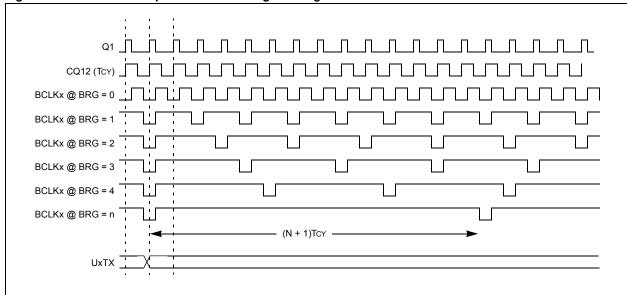

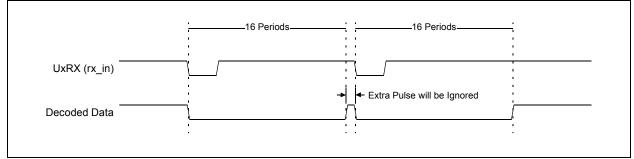

# 21.3.1 BCLKx Output

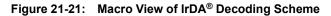

The BCLKx pin will output the 16x baud clock if the UARTx and BCLKx output are enabled (UEN<1:0> = 11). This feature is used for external IrDA encoder/decoder support (refer to Figure 21-2). BCLKx output stays low during Sleep mode. BCLKx is forced as an output as long as UARTx is kept in this mode (UEN<1:0> = 11), irrespective of PORTx and TRISx latch bits.

## 21.3.2 Baud Rate Tables

UART baud rates are provided in Table 21-1 and Table 21-2 for common device instruction cycle frequencies (Fcy). The minimum and maximum baud rates for each frequency are also shown.

Table 21-1:UART Baud Rates (BRGH = 0)

|           |                     | Fcy = 16 MHz |                        |                     | Fcy = 12 MHz |                        |

|-----------|---------------------|--------------|------------------------|---------------------|--------------|------------------------|

| BAUD RATE | Actual Baud<br>Rate | % Error      | BRG Value<br>(Decimal) | Actual Baud<br>Rate | % Error      | BRG Value<br>(Decimal) |

| 110       | 110.0               | 0.00         | 9090                   | 110.0               | 0.00         | 6817                   |

| 300       | 300.0               | 0.01         | 3332                   | 300.0               | 0.00         | 2499                   |

| 1200      | 1200.5              | 0.04         | 832                    | 1200.0              | 0.00         | 624                    |

| 2400      | 2398.1              | -0.08        | 416                    | 2403.8              | 0.16         | 311                    |

| 9600      | 9615.4              | 0.16         | 103                    | 9615.3              | 0.16         | 77                     |

| 19.2K     | 19230.8             | 0.16         | 51                     | 19230.7             | 0.15         | 38                     |

| 38.4K     | 38461.5             | 0.16         | 25                     | 37500.0             | -2.34        | 19                     |

| 56K       | 55555.6             | -0.79        | 17                     | 57692.3             | -3.02        | 12                     |

| 115K      | 111111.1            | -3.38        | 8                      |                     |              |                        |

| 250K      | 250000.0            | 0.00         | 3                      |                     |              |                        |

| 300K      |                     |              |                        |                     |              |                        |

| 500K      | 500000.0            | 0.00         | 1                      |                     |              |                        |

| Min.      | 15.0                | 0.00         | 65535                  | 11.0                | 0.00         | 65535                  |

| Max.      | 1000000.0           | 0.00         | 0                      | 480000.0            | 0.00         | 0                      |

|           |                     | FCY = 8 MHz | <u>.</u>               |                     | Fcy = 4 MHz | 2                      |                     | Fcy = 1 MHz | <u>.</u>               |

|-----------|---------------------|-------------|------------------------|---------------------|-------------|------------------------|---------------------|-------------|------------------------|

| BAUD RATE | Actual<br>Baud Rate | % Error     | BRG Value<br>(Decimal) | Actual<br>Baud Rate | % Error     | BRG Value<br>(Decimal) | Actual<br>Baud Rate | % Error     | BRG Value<br>(Decimal) |

| 110       | 917.4               | 0.00        | 4544                   | 110.0               | 0.00        | 2272                   | 110.0               | 0.00        | 567                    |

| 300       | 299.9               | 0.00        | 1666                   | 300.1               | 0.00        | 832                    | 300.4               | 0.10        | 207                    |

| 1200      | 1199.0              | 0.00        | 416                    | 1201.9              | 0.16        | 207                    | 1201.9              | 0.16        | 51                     |

| 2400      | 2403.8              | 0.16        | 207                    | 2403.8              | 0.15        | 103                    | 2403.8              | 0.15        | 25                     |

| 9600      | 9615.4              | 0.16        | 51                     | 9615.4              | 0.20        | 25                     |                     |             |                        |

| 19.2K     | 19230.8             | 0.16        | 25                     | 19230.8             | 0.20        | 12                     |                     |             |                        |

| 38.4K     | 38461.5             | 0.16        | 12                     |                     |             |                        |                     |             |                        |

| 56K       | 55555.6             | -0.79       | 8                      |                     |             |                        |                     |             |                        |

| 115K      |                     |             |                        |                     |             |                        |                     |             |                        |

| 250K      |                     |             |                        |                     |             |                        |                     |             |                        |

| 300K      |                     |             |                        |                     |             |                        |                     |             |                        |

| 500K      |                     |             |                        |                     |             |                        |                     |             |                        |

| Min.      | 8.0                 | 0.00        | 65535                  | 4.0                 | 0.00        | 65535                  | 0.95                | 0.00        | 65535                  |

| Max.      | 500000.0            | 0.00        | 0                      | 250000.0            | 0.00        | 0                      | 62500.0             | 0.00        | 0                      |

|           |                     | Fcy = 16 MHz |                        |                     | Fcy = 12 MHz |                        |

|-----------|---------------------|--------------|------------------------|---------------------|--------------|------------------------|

| BAUD RATE | Actual Baud<br>Rate | % Error      | BRG Value<br>(Decimal) | Actual Baud<br>Rate | % Error      | BRG Value<br>(Decimal) |

| 110       | 110.0               | 0.00         | 36363                  | 110.0               | 0.00         | 27272                  |

| 300       | 300.0               | 0.01         | 13332                  | 300.0               | 0.00         | 9999                   |

| 1200      | 1200.1              | 0.01         | 3332                   | 1200.0              | 0.00         | 2499                   |

| 2400      | 2399.5              | -0.01        | 1666                   | 2403.8              | 0.00         | 1249                   |

| 9600      | 9592.3              | -0.07        | 416                    | 9584.6              | -0.15        | 312                    |

| 19.2K     | 19230.7             | 0.16         | 207                    | 19230.7             | 0.15         | 155                    |

| 38.4K     | 38461.5             | 0.16         | 103                    | 38461.5             | 0.16         | 77                     |

| 56K       | 56338.0             | 0.60         | 70                     | 55555.5             | -0.79        | 53                     |

| 115K      | 114285.7            | -0.62        | 34                     | 115384.0            | 0.33         | 25                     |

| 250K      | 250000.0            | 0.00         | 15                     |                     |              |                        |

| 300K      | 307692.3            | 2.50         | 12                     |                     |              |                        |

| 500K      | 500000.0            | 0.00         | 7                      |                     |              |                        |

| Min.      | 61.0                | 0.00         | 65535                  | 46.0                | 0.00         | 65535                  |

| Max.      | 4000000.0           | 0.00         | 0                      | 300000.0            | 0.00         | 0                      |

### Table 21-2: UART Baud Rates (BRGH = 1)

|           |                     | FCY = 8 MHz | 2                      |                     | Fcy = 4MHz | :                      |                     | Fcy = 1 MHz | <u>.</u>               |

|-----------|---------------------|-------------|------------------------|---------------------|------------|------------------------|---------------------|-------------|------------------------|

| BAUD RATE | Actual<br>Baud Rate | % Error     | BRG Value<br>(Decimal) | Actual<br>Baud Rate | % Error    | BRG Value<br>(Decimal) | Actual<br>Baud Rate | % Error     | BRG Value<br>(Decimal) |

| 110       | 110.0               | 0.00        | 18181                  | 110.0               | 0.00       | 9090                   | 110.0               | 0.00        | 2272                   |

| 300       | 300.0               | 0.00        | 6666                   | 300.0               | 0.00       | 3332                   | 300.1               | 0.10        | 832                    |

| 1200      | 1199.7              | -0.01       | 1666                   | 1200.5              | 0.00       | 832                    | 1201.9              | 0.15        | 207                    |

| 2400      | 2400.9              | 0.04        | 832                    | 2398.1              | -0.07      | 416                    | 2403.8              | 0.15        | 103                    |

| 9600      | 9615.4              | 0.16        | 207                    | 9615.3              | 0.16       | 103                    | 9615.3              | 0.16        | 25                     |

| 19.2K     | 19230.8             | 0.16        | 103                    | 19230.7             | 0.16       | 51                     | 19230.7             | 0.16        | 12                     |

| 38.4K     | 38461.5             | 0.16        | 51                     | 38461.5             | 0.16       | 25                     |                     |             |                        |

| 56K       | 55555.6             | -0.79       | 35                     | 55555.5             | -0.79      | 17                     |                     |             |                        |

| 115K      | 117647.0            | 2.30        | 16                     |                     |            |                        |                     |             |                        |

| 250K      |                     |             |                        |                     |            |                        |                     |             |                        |

| 300K      |                     |             |                        |                     |            |                        |                     |             |                        |

| 500K      |                     |             |                        |                     |            |                        |                     |             |                        |

| Min.      | 31.0                | 0.00        | 65535                  | 16.0                | 0.00       | 65535                  | 3.81                | 0.00        | 65535                  |

| Max.      | 200000.0            | 0.00        | 0                      | 1000000.0           | 0.00       | 0                      | 250000.0            | 0.00        | 0                      |

# 21.4 UART CONFIGURATION

The UART uses standard Non-Return-to-Zero (NRZ) format (one Start bit, eight or nine data bits and one or two Stop bits). Parity is supported by the hardware and may be configured by the user as even, odd or no parity. The most common data format is 8 bits, no parity and one Stop bit (denoted as 8, N, 1), which is the default (POR) setting. The number of data bits and Stop bits and the parity, are specified in the PDSEL<1:0> (UxMODE<2:1>) and STSEL (UxMODE<0>) bits. An on-chip, dedicated, 16-bit Baud Rate Generator can be used to derive standard baud rate frequencies from the oscillator. The UART transmits and receives the LSb first. The UART module's transmitter and receiver are functionally independent but use the same data format and baud rate.

# 21.4.1 Enabling the UART

The UART module is enabled by setting the UARTEN (UxMODE<15>) bit and UTXEN (UxSTA<10>) bit. Once enabled, the UxTX and UxRX pins are configured as an output and an input, respectively, overriding the TRIS and PORT register bit settings for the corresponding I/O port pins. The UxTX pin is at logic '1' when no transmission is taking place.

**Note:** The UTXEN bit should not be set until the UARTEN bit has been set; otherwise, UART transmissions will not be enabled.

## 21.4.2 Disabling the UART

The UART module is disabled by clearing the UARTEN (UxMODE<15>) bit. This is the default state after any Reset. If the UART is disabled, all UART pins operate as port pins under the control of their corresponding PORT and TRIS bits.

Disabling the UART module resets the buffers to empty states. Any data characters in the buffers are lost and the baud rate counter is reset.

All error and status flags associated with the UART module are reset when the module is disabled. The URXDA, OERR, FERR, PERR, UTXEN, UTXBRK and UTXBF bits are cleared, whereas RIDLE and TRMT are set. Other control bits, including ADDEN, URXISEL<1:0>, UTXISEL<1:0>, as well as the UXMODE and UXBRG registers, are not affected.

Clearing the UARTEN bit while the UART is active will abort all pending transmissions and receptions and reset the module as defined above. Re-enabling the UART will restart the UART in the same configuration.

## 21.4.3 Alternate UART I/O Pins

Some PIC24F devices have an alternate set of UART transmit and receive pins that can be used for communications. The alternate UART pins are useful when the primary UART pins are shared by other peripherals. The alternate I/O pins are enabled by setting the ALTIO bit (UxMODE<10>). If ALTIO = 1, the UxATX and UxARX pins (alternate transmit and alternate receive pins, respectively) are used by the UART module instead of the UxTX and UxRX pins. If ALTIO = 0, the UxTX and UxRX pins are used by the UART module.

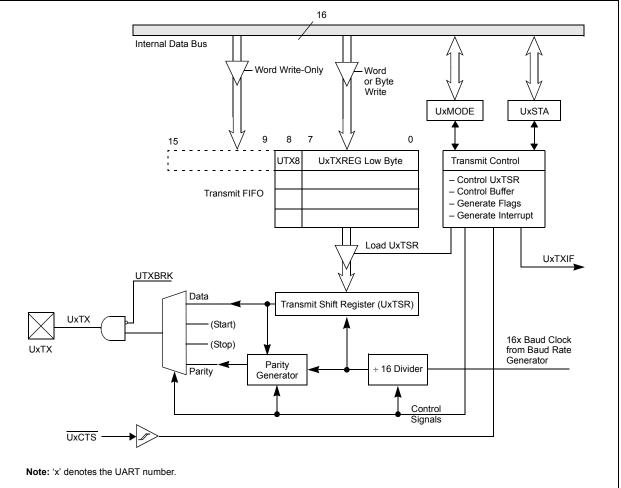

# 21.5 UART TRANSMITTER

The UART transmitter block diagram is shown in Figure 21-3. The heart of the transmitter is the Transmit Shift Register (UxTSR). The Shift register obtains its data from the transmit FIFO buffer, UxTXREG. The UxTXREG register is loaded with data in software. The UxTSR register is not loaded until the Stop bit has been transmitted from the previous load. As soon as the Stop bit is transmitted, the UxTSR is loaded with new data from the UxTXREG register (if available).

**Note:** The UxTSR register is not mapped in data memory, so it is not available to the user.

Transmission is enabled by setting the UTXEN enable bit (UxSTA<10>). The actual transmission will not occur until the UxTXREG register has been loaded with data and the Baud Rate Generator (UxBRG) has produced a shift clock (Figure 21-3). The transmission can also be started by first loading the UxTXREG register and then setting the UTXEN enable bit. Normally, when transmission is first started, the UxTSR register is empty, so a transfer to the UxTXREG register will result in an immediate transfer to UxTSR. Clearing the UTXEN bit during a transmission will cause the transmission to be aborted and will reset the transmitter. As a result, the UxTX pin will revert to a high-impedance state.

**Note:** There should be a minimum 1 clock cycle delay between setting the UARTEN bit and writing data to UxTXREG. This ensures that the transmit line is held idle for an appropriate amount of time before the transmission begins.

In order to select 9-bit transmission, the PDSEL<1:0> bits (UxMODE<2:1>) should be set to '11' and the ninth bit should be written to the UTX8 bit (UxTXREG<8>). A word write should be performed to UxTXREG so that all nine bits are written at the same time.

**Note:** There is no parity in the case of 9-bit data transmission.

# 21.5.1 Transmit Buffer (UxTXREG)

The transmit buffer is 9 bits wide and 4 levels deep. Together with the Transmit Shift Registers (UxTSR), the user effectively has a 5-level deep buffer. It is organized as First-In-First-Out (FIFO). Once the UxTXREG contents are transferred to the UxTSR register, the current buffer location becomes available for new data to be written and the next buffer location is sourced to the UxTSR register. The UTXBF (UxSTA<9>) status bit is set whenever the buffer is full. If a user attempts to write to a full buffer, the new data will not be accepted into the FIFO.

The FIFO is reset during any device Reset, but is not affected when the device enters a Power-Saving mode or wakes up from a Power-Saving mode.

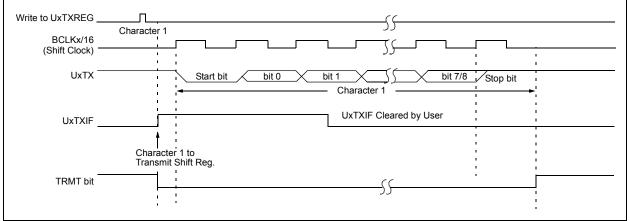

## 21.5.2 Transmit Interrupt

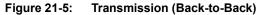

The Transmit Interrupt Flag (UxTXIF) is located in the corresponding Interrupt Flag Status (IFSx) register. The UTXISEL<1:0> control bits (UxSTA<15,13>) determine when the UART will generate a transmit interrupt.

- 1. UTXISEL<1:0> = 00, the UxTXIF is set when a character is transferred from the transmit buffer to the Transmit Shift Register (UxTSR). This implies at least one location is empty in the transmit buffer.

- 2. UTXISEL<1:0> = 01, the UxTXIF is set when the last character is shifted out of the Transmit Shift Register (UxTSR). This implies that all the transmit operations are completed.

- 3. UTXISEL<1:0> = 10, the UxTXIF is set when the character is transferred to the Transmit Shift Register (UxTSR) and the transmit buffer is empty.

# The UxTXIF bit will be set when the module is first enabled. The user should clear the UxTXIF bit in the ISR.

Switching between the two Interrupt modes during operation is possible.

**Note:** When the UTXEN bit is set, the UxTXIF flag bit will also be set, after two cycles, if UTXISEL<1:0> = 00, since the transmit buffer is not yet full (can move transmit data to the UxTXREG register).

While the UxTXIF flag bit indicates the status of the UxTXREG register, the TRMT bit (UxSTA<8>) shows the status of the UxTSR. The TRMT status bit is a read-only bit, which is set when the UxTSR is empty. No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the UxTSR is empty.

# 21.5.3 Setup for UART Transmit

Steps to follow when setting up a transmission:

- 1. Initialize the UxBRG register for the appropriate baud rate (see Section 21.3 "UART Baud Rate Generator (BRG)").

- 2. Set the number of data bits, number of Stop bits and parity selection by writing to the PDSEL<1:0> (UxMODE<2:1>) and STSEL (UxMODE<0>) bits.

- If transmit interrupts are desired, set the UxTXIE control bit in the corresponding Interrupt Enable Control register (IECx). Specify the interrupt priority for the transmit interrupt using the UxTXIP<2:0> control bits in the corresponding Interrupt Priority Control register (IPCx). Also, select the Transmit Interrupt mode by writing the UTXISEL<1:0> (UxSTA<15,13>) bits.

- 4. Enable the UART module by setting the UARTEN (UxMODE<15>) bit.

- Enable the transmission by setting the UTXEN (UxSTA<10>) bit, which will also set the UxTXIF bit. The UxTXIF bit should be cleared in the software routine that services the UART transmit interrupt. The operation of the UxTXIF bit is controlled by the UTXISEL<1:0> control bits.

- Load data to the UxTXREG register (starts transmission). If 9-bit transmission has been selected, load a word. If 8-bit transmission is used, load a byte. Data can be loaded into the buffer until the UTXBF status bit (UxSTA<9>) is set.

**Note:** The UTXEN bit should not be set until the UARTEN bit has been set; otherwise, UART transmissions will not be enabled.

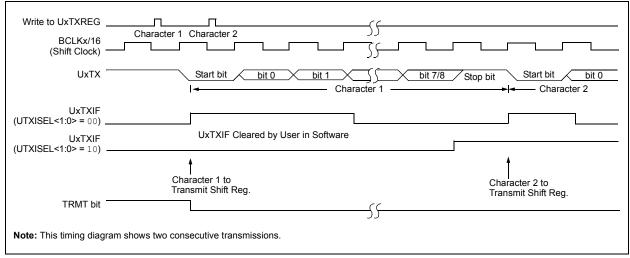

# 21.5.4 Transmission of Break Characters

A Break character transmit consists of a Start bit, followed by twelve bits of '0' and a Stop bit. A Frame Break character is sent whenever the UTXBRK and UTXEN bits are set while the Transmit Shift Register is loaded with data. A dummy write to the UxTXREG register is necessary to initiate the Break character transmission. Note that the data value written to the UxTXREG for the Break character is ignored. The write simply serves the purpose of initiating the proper sequence – all '0's will be transmitted.

The UTXBRK bit is automatically reset by hardware after the corresponding Stop bit is sent. This allows the user to preload the transmit FIFO with the next transmit byte following the Break character (typically, the Sync character in the LIN specification).

**Note:** The user should wait for the transmitter to be Idle (TRMT = 1) before setting the UTXBRK. The UTXBRK overrides any other transmitter activity. If the user clears the UTXBRK bit prior to sequence completion, unexpected module behavior can result. Sending a Break character does not generate a transmit interrupt.

The TRMT bit indicates when the Transmit Shift Register is empty or full, just as it does during normal transmission. See Figure 21-6 for the timing of the Break character sequence.

Figure 21-6: Send Break Character Sequence

#### 21.5.4.1 BREAK AND SYNC TRANSMIT SEQUENCE

The following sequence will send a message frame header made up of a Break, followed by an auto-baud Sync byte. This sequence is typical of a LIN bus master.

- 1. Configure the UART for the desired mode.

- 2. Set UTXEN and UTXBRK sets up the Break character.

- 3. Load the UxTXREG with a dummy character to initiate transmission (value is ignored).

- 4. Write '55h' to UxTXREG loads Sync character into the transmit FIFO.

After the Break has been sent, the UTXBRK bit is reset by hardware. The Sync character now transmits.

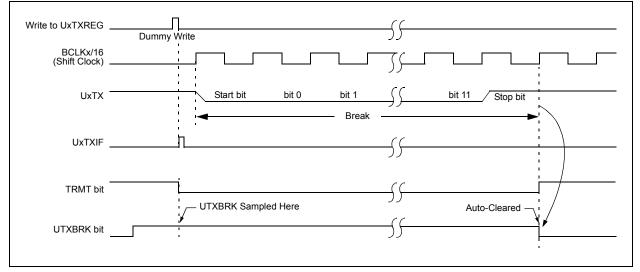

# 21.6 UART RECEIVER

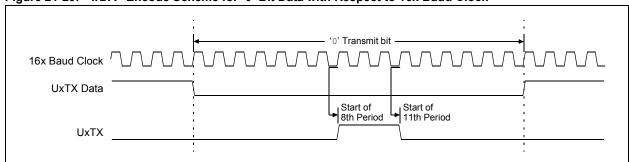

The receiver block diagram is shown in Figure 21-7. The heart of the receiver is the Receive (Serial) Shift Register (UxRSR). The data is received on the UxRX pin and is sent to the data recovery block. The data recovery block operates at 16 times the baud rate, whereas the main receive serial shifter operates at the baud rate. After sampling the UxRX pin for the Stop bit, the received data in UxRSR is transferred to the receive FIFO (if it is empty).

**Note:** The UxRSR register is not mapped in data memory, so it is not available to the user.

The data on the UxRX pin is sampled three times by a majority detect circuit to determine if a high or a low level is present at the UxRX pin.

### 21.6.1 Receive Buffer (UxRXREG)

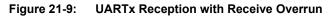

The UART receiver has a 4-deep, 9-bit wide FIFO receive data buffer. UxRXREG is a memory mapped register that provides access to the output of the FIFO. It is possible for 4 words of data to be received and transferred to the FIFO and a fifth word to begin shifting to the UxRSR register before a buffer overrun occurs.

### 21.6.2 Receiver Error Handling

If the FIFO is full (four characters) and a fifth character is fully received into the UxRSR register, the Overrun Error bit, OERR (UxSTA<1>), will be set. The word in UxRSR will be kept, but further transfers to the receive FIFO are inhibited as long as the OERR bit is set. The user must clear the OERR bit in software to allow further data to be received.

If it is desired to keep the data received prior to the overrun, the user should first read all five characters, then clear the OERR bit. If the five characters can be discarded, the user can simply clear the OERR bit. This effectively resets the receive FIFO and all prior received data is lost.

**Note:** The data in the receive FIFO should be read prior to clearing the OERR bit. The FIFO is reset when OERR is cleared which causes all data in the buffer to be lost.

The Framing Error bit, FERR (UxSTA<2>), is set if a Stop bit is detected at a logic low level.

The Parity Error bit, PERR (UxSTA<3>), is set if a parity error has been detected in the data word at the top of the buffer (i.e., the current word). For example, a parity error would occur if the parity is set to be even, but the total number of ones in the data has been detected to be odd. The PERR bit is irrelevant in the 9-bit mode. The FERR and PERR bits are buffered along with the corresponding word and should be read before reading the data word.

An interrupt is generated if any of these (OERR, FERR and PERR) errors occur. This generated interrupt will be valid for only one cycle. The user will have to enable the corresponding Interrupt Enable Control bit (IEC4<UxERIE>) to go to the corresponding interrupt vector location.

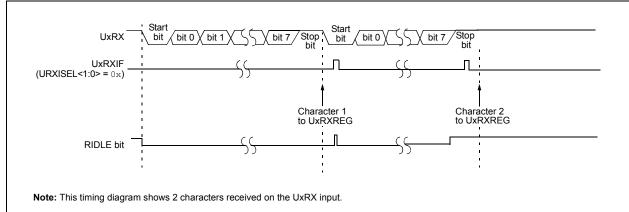

## 21.6.3 Receive Interrupt

The UARTx Receive Interrupt Flag (UxRXIF) is located in the corresponding Interrupt Flag Status (IFSx) register. The URXISEL<1:0> (UxSTA<7:6>) control bits determine when the UART receiver generates an interrupt.

- a) If URXISEL<1:0> = 00 or 01, an interrupt is generated each time a data word is transferred from the Receive Shift Register (UxRSR) to the receive buffer. There may be one or more characters in the receive buffer.

- b) If URXISEL<1:0> = 10, an interrupt is generated when a word is transferred from the Receive Shift Register (UxRSR) to the receive buffer, and as a result, the receive buffer contains 3 or 4 characters.

- c) If URXISEL<1:0> = 11, an interrupt is generated when a word is transferred from the Receive Shift Register (UxRSR) to the receive buffer, and as a result, the receive buffer contains 4 characters (i.e., becomes full).

Switching between the three Interrupt modes during operation is possible.

While the URXDA and UxRXIF flag bits indicate the status of the UxRXREG register, the RIDLE bit (UxSTA<4>) shows the status of the UxRSR register. The RIDLE status bit is a read-only bit which is set when the receiver is Idle (i.e., the UxRSR register is empty). No interrupt logic is tied to this bit, so the user has to poll this bit in order to determine if the UxRSR is Idle.

The URXDA bit (UxSTA<0>) indicates whether the receive buffer has data or whether the buffer is empty. This bit is set as long as there is at least one character to be read from the receive buffer. URXDA is a read-only bit.

Figure 21-7 shows a block diagram of the UARTx receiver.

# 21.6.4 Setup for UART Reception

Steps to follow when setting up a reception:

- 1. Initialize the UxBRG register for the appropriate baud rate (see Section 21.3 "UART Baud Rate Generator (BRG)").

- 2. Set the number of data bits, number of Stop bits and parity selection by writing to the PDSEL<1:0> (UxMODE<2:1>) and STSEL (UxMODE<0>) bits.

- 3. If interrupts are desired, then set the UxRXIE bit in the corresponding Interrupt Enable Control (IECx) register. Specify the interrupt priority for the interrupt using the UxRXIP<2:0> control bits in the corresponding Interrupt Priority Control register (IPCx). Also, select the Receive Interrupt mode by writing to the URXISEL<1:0> (UxSTA<7:6>) bits.

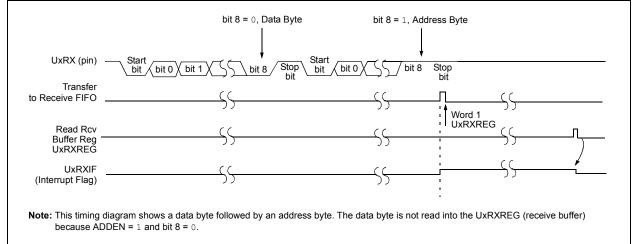

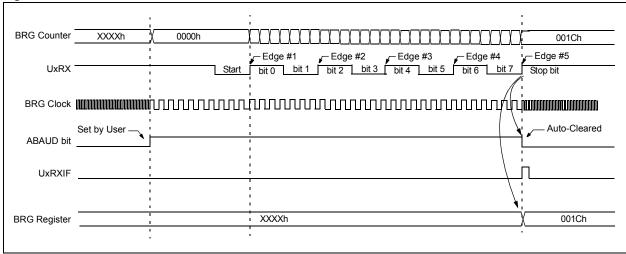

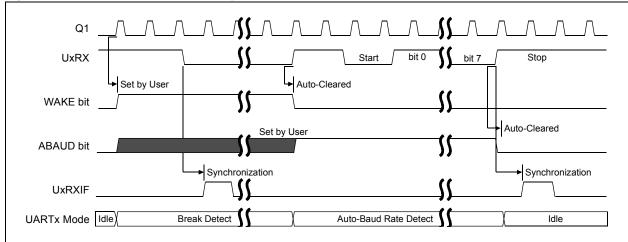

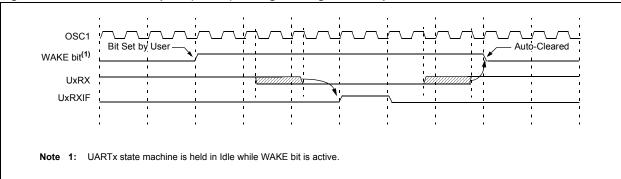

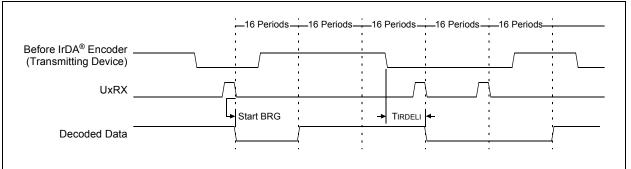

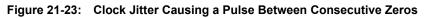

- 4. Enable the UART module by setting the UARTEN (UxMODE<15>) bit.